STM32F429 on-chip ETHERNET module class header file. More...

#include "lwip/init.h"#include "lwip/netif.h"#include "netif/ethernet.h"#include "stm32f429xx.h"#include "Communication_Link.h"

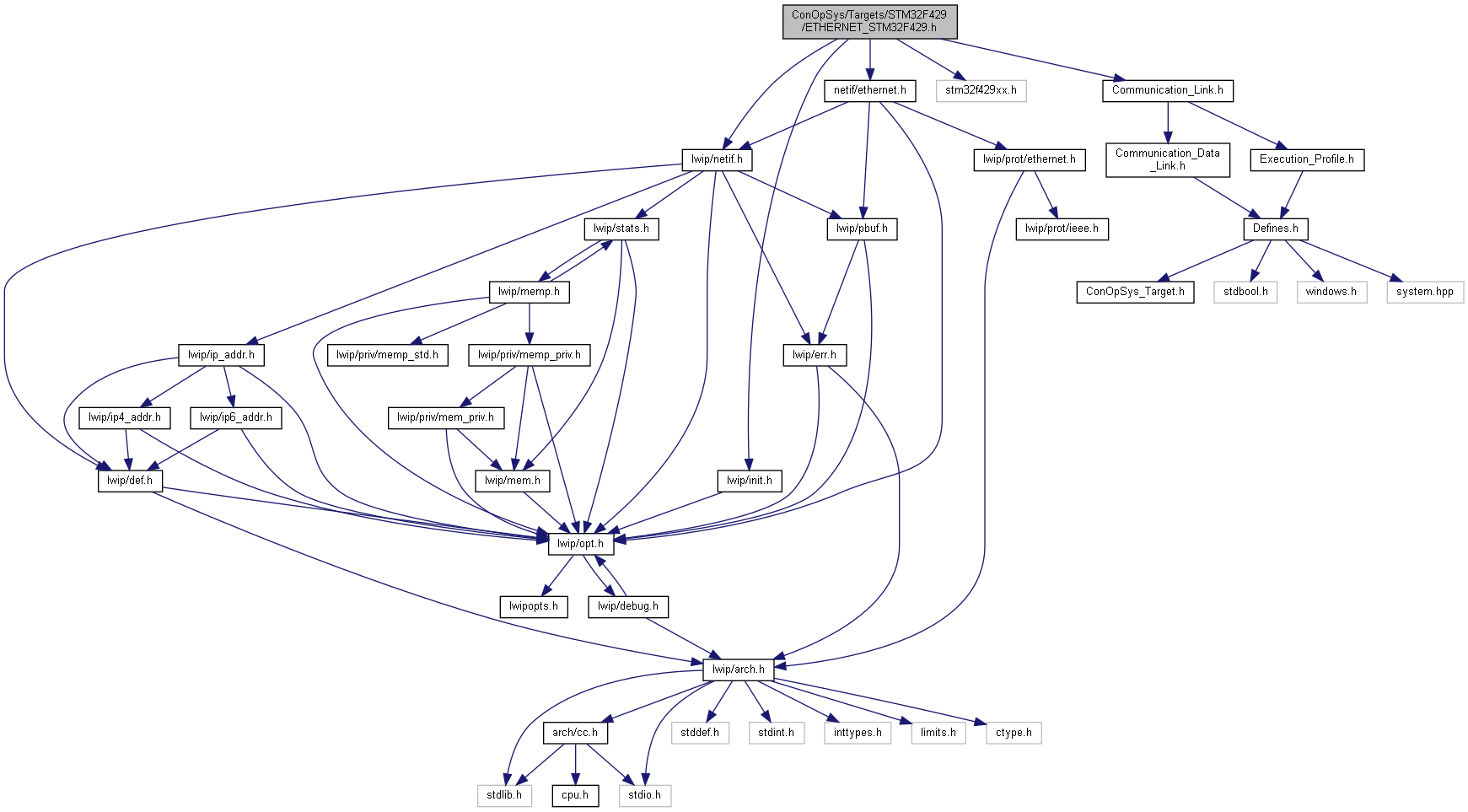

Include dependency graph for ETHERNET_STM32F429.h:

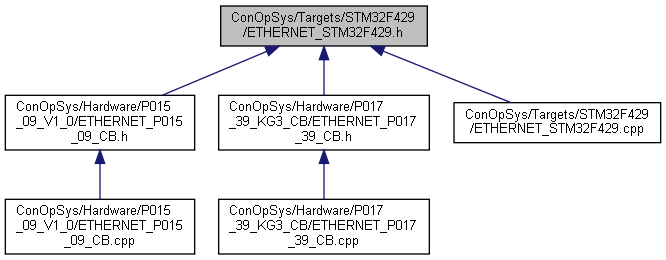

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | ETH_InitTypeDef |

| struct | ETH_DMADescTypeDef |

| struct | ETH_DMARxFrameInfos |

| Received Frame Informations structure definition. More... | |

| struct | ETH_MACInitTypeDef |

| ETH MAC Configuration Structure definition. More... | |

| struct | ETH_DMAInitTypeDef |

| ETH DMA Configuration Structure definition. More... | |

| struct | ETH_HandleTypeDef |

| class | TETHERNET_STM32F429 |

| STM32F429 on-chip ETHERNET hardware abstraction layer class. More... | |

Macros | |

| #define | ETH_MAX_PACKET_SIZE 1524U |

| #define | ETH_HEADER 14U |

| #define | ETH_CRC 4U |

| #define | ETH_EXTRA 2U |

| #define | ETH_VLAN_TAG 4U |

| #define | ETH_MIN_ETH_PAYLOAD 46U |

| #define | ETH_MAX_ETH_PAYLOAD 1500U |

| #define | ETH_JUMBO_FRAME_PAYLOAD 9000U |

| #define | ETH_DMATXDESC_OWN 0x80000000U |

| Bit definition of TDES0 register: DMA Tx descriptor status register. More... | |

| #define | ETH_DMATXDESC_IC 0x40000000U |

| #define | ETH_DMATXDESC_LS 0x20000000U |

| #define | ETH_DMATXDESC_FS 0x10000000U |

| #define | ETH_DMATXDESC_DC 0x08000000U |

| #define | ETH_DMATXDESC_DP 0x04000000U |

| #define | ETH_DMATXDESC_TTSE 0x02000000U |

| #define | ETH_DMATXDESC_CIC 0x00C00000U |

| #define | ETH_DMATXDESC_CIC_BYPASS 0x00000000U |

| #define | ETH_DMATXDESC_CIC_IPV4HEADER 0x00400000U |

| #define | ETH_DMATXDESC_CIC_TCPUDPICMP_SEGMENT 0x00800000U |

| #define | ETH_DMATXDESC_CIC_TCPUDPICMP_FULL 0x00C00000U |

| #define | ETH_DMATXDESC_TER 0x00200000U |

| #define | ETH_DMATXDESC_TCH 0x00100000U |

| #define | ETH_DMATXDESC_TTSS 0x00020000U |

| #define | ETH_DMATXDESC_IHE 0x00010000U |

| #define | ETH_DMATXDESC_ES 0x00008000U |

| #define | ETH_DMATXDESC_JT 0x00004000U |

| #define | ETH_DMATXDESC_FF 0x00002000U |

| #define | ETH_DMATXDESC_PCE 0x00001000U |

| #define | ETH_DMATXDESC_LCA 0x00000800U |

| #define | ETH_DMATXDESC_NC 0x00000400U |

| #define | ETH_DMATXDESC_LCO 0x00000200U |

| #define | ETH_DMATXDESC_EC 0x00000100U |

| #define | ETH_DMATXDESC_VF 0x00000080U |

| #define | ETH_DMATXDESC_CC 0x00000078U |

| #define | ETH_DMATXDESC_ED 0x00000004U |

| #define | ETH_DMATXDESC_UF 0x00000002U |

| #define | ETH_DMATXDESC_DB 0x00000001U |

| #define | ETH_DMATXDESC_TBS2 0x1FFF0000U |

| Bit definition of TDES1 register. More... | |

| #define | ETH_DMATXDESC_TBS1 0x00001FFFU |

| #define | ETH_DMATXDESC_B1AP 0xFFFFFFFFU |

| Bit definition of TDES2 register. More... | |

| #define | ETH_DMATXDESC_B2AP 0xFFFFFFFFU |

| Bit definition of TDES3 register. More... | |

| #define | ETH_DMAPTPTXDESC_TTSL 0xFFFFFFFFU /* Transmit Time Stamp Low */ |

| #define | ETH_DMAPTPTXDESC_TTSH 0xFFFFFFFFU /* Transmit Time Stamp High */ |

| #define | ETH_DMARXDESC_OWN 0x80000000U |

| Bit definition of RDES0 register: DMA Rx descriptor status register. More... | |

| #define | ETH_DMARXDESC_AFM 0x40000000U |

| #define | ETH_DMARXDESC_FL 0x3FFF0000U |

| #define | ETH_DMARXDESC_ES 0x00008000U |

| #define | ETH_DMARXDESC_DE 0x00004000U |

| #define | ETH_DMARXDESC_SAF 0x00002000U |

| #define | ETH_DMARXDESC_LE 0x00001000U |

| #define | ETH_DMARXDESC_OE 0x00000800U |

| #define | ETH_DMARXDESC_VLAN 0x00000400U |

| #define | ETH_DMARXDESC_FS 0x00000200U |

| #define | ETH_DMARXDESC_LS 0x00000100U |

| #define | ETH_DMARXDESC_IPV4HCE 0x00000080U |

| #define | ETH_DMARXDESC_LC 0x00000040U |

| #define | ETH_DMARXDESC_FT 0x00000020U |

| #define | ETH_DMARXDESC_RWT 0x00000010U |

| #define | ETH_DMARXDESC_RE 0x00000008U |

| #define | ETH_DMARXDESC_DBE 0x00000004U |

| #define | ETH_DMARXDESC_CE 0x00000002U |

| #define | ETH_DMARXDESC_MAMPCE 0x00000001U |

| #define | ETH_DMARXDESC_DIC 0x80000000U |

| Bit definition of RDES1 register. More... | |

| #define | ETH_DMARXDESC_RBS2 0x1FFF0000U |

| #define | ETH_DMARXDESC_RER 0x00008000U |

| #define | ETH_DMARXDESC_RCH 0x00004000U |

| #define | ETH_DMARXDESC_RBS1 0x00001FFFU |

| #define | ETH_DMARXDESC_B1AP 0xFFFFFFFFU |

| Bit definition of RDES2 register. More... | |

| #define | ETH_DMARXDESC_B2AP 0xFFFFFFFFU |

| Bit definition of RDES3 register. More... | |

| #define | ETH_DMAPTPRXDESC_PTPV 0x00002000U /* PTP Version */ |

| #define | ETH_DMAPTPRXDESC_PTPFT 0x00001000U /* PTP Frame Type */ |

| #define | ETH_DMAPTPRXDESC_PTPMT 0x00000F00U /* PTP Message Type */ |

| #define | ETH_DMAPTPRXDESC_PTPMT_SYNC 0x00000100U /* SYNC message (all clock types) */ |

| #define | ETH_DMAPTPRXDESC_PTPMT_FOLLOWUP 0x00000200U /* FollowUp message (all clock types) */ |

| #define | ETH_DMAPTPRXDESC_PTPMT_DELAYREQ 0x00000300U /* DelayReq message (all clock types) */ |

| #define | ETH_DMAPTPRXDESC_PTPMT_DELAYRESP 0x00000400U /* DelayResp message (all clock types) */ |

| #define | ETH_DMAPTPRXDESC_PTPMT_PDELAYREQ_ANNOUNCE 0x00000500U /* PdelayReq message (peer-to-peer transparent clock) or Announce message (Ordinary or Boundary clock) */ |

| #define | ETH_DMAPTPRXDESC_PTPMT_PDELAYRESP_MANAG 0x00000600U /* PdelayResp message (peer-to-peer transparent clock) or Management message (Ordinary or Boundary clock) */ |

| #define | ETH_DMAPTPRXDESC_PTPMT_PDELAYRESPFOLLOWUP_SIGNAL 0x00000700U /* PdelayRespFollowUp message (peer-to-peer transparent clock) or Signaling message (Ordinary or Boundary clock) */ |

| #define | ETH_DMAPTPRXDESC_IPV6PR 0x00000080U /* IPv6 Packet Received */ |

| #define | ETH_DMAPTPRXDESC_IPV4PR 0x00000040U /* IPv4 Packet Received */ |

| #define | ETH_DMAPTPRXDESC_IPCB 0x00000020U /* IP Checksum Bypassed */ |

| #define | ETH_DMAPTPRXDESC_IPPE 0x00000010U /* IP Payload Error */ |

| #define | ETH_DMAPTPRXDESC_IPHE 0x00000008U /* IP Header Error */ |

| #define | ETH_DMAPTPRXDESC_IPPT 0x00000007U /* IP Payload Type */ |

| #define | ETH_DMAPTPRXDESC_IPPT_UDP 0x00000001U /* UDP payload encapsulated in the IP datagram */ |

| #define | ETH_DMAPTPRXDESC_IPPT_TCP 0x00000002U /* TCP payload encapsulated in the IP datagram */ |

| #define | ETH_DMAPTPRXDESC_IPPT_ICMP 0x00000003U /* ICMP payload encapsulated in the IP datagram */ |

| #define | ETH_DMAPTPRXDESC_RTSL 0xFFFFFFFFU /* Receive Time Stamp Low */ |

| #define | ETH_DMAPTPRXDESC_RTSH 0xFFFFFFFFU /* Receive Time Stamp High */ |

| #define | ETH_AUTONEGOTIATION_ENABLE 0x00000001U |

| #define | ETH_AUTONEGOTIATION_DISABLE 0x00000000U |

| #define | ETH_SPEED_10M 0x00000000U |

| #define | ETH_SPEED_100M 0x00004000U |

| #define | ETH_MODE_FULLDUPLEX 0x00000800U |

| #define | ETH_MODE_HALFDUPLEX 0x00000000U |

| #define | ETH_RXPOLLING_MODE 0x00000000U |

| #define | ETH_RXINTERRUPT_MODE 0x00000001U |

| #define | ETH_CHECKSUM_BY_HARDWARE 0x00000000U |

| #define | ETH_CHECKSUM_BY_SOFTWARE 0x00000001U |

| #define | ETH_MEDIA_INTERFACE_MII 0x00000000U |

| #define | ETH_MEDIA_INTERFACE_RMII ((uint32_t)SYSCFG_PMC_MII_RMII_SEL) |

| #define | ETH_WATCHDOG_ENABLE 0x00000000U |

| #define | ETH_WATCHDOG_DISABLE 0x00800000U |

| #define | ETH_JABBER_ENABLE 0x00000000U |

| #define | ETH_JABBER_DISABLE 0x00400000U |

| #define | ETH_INTERFRAMEGAP_96BIT 0x00000000U |

| #define | ETH_INTERFRAMEGAP_88BIT 0x00020000U |

| #define | ETH_INTERFRAMEGAP_80BIT 0x00040000U |

| #define | ETH_INTERFRAMEGAP_72BIT 0x00060000U |

| #define | ETH_INTERFRAMEGAP_64BIT 0x00080000U |

| #define | ETH_INTERFRAMEGAP_56BIT 0x000A0000U |

| #define | ETH_INTERFRAMEGAP_48BIT 0x000C0000U |

| #define | ETH_INTERFRAMEGAP_40BIT 0x000E0000U |

| #define | ETH_CARRIERSENCE_ENABLE 0x00000000U |

| #define | ETH_CARRIERSENCE_DISABLE 0x00010000U |

| #define | ETH_RECEIVEOWN_ENABLE 0x00000000U |

| #define | ETH_RECEIVEOWN_DISABLE 0x00002000U |

| #define | ETH_LOOPBACKMODE_ENABLE 0x00001000U |

| #define | ETH_LOOPBACKMODE_DISABLE 0x00000000U |

| #define | ETH_CHECKSUMOFFLAOD_ENABLE 0x00000400U |

| #define | ETH_CHECKSUMOFFLAOD_DISABLE 0x00000000U |

| #define | ETH_RETRYTRANSMISSION_ENABLE 0x00000000U |

| #define | ETH_RETRYTRANSMISSION_DISABLE 0x00000200U |

| #define | ETH_AUTOMATICPADCRCSTRIP_ENABLE 0x00000080U |

| #define | ETH_AUTOMATICPADCRCSTRIP_DISABLE 0x00000000U |

| #define | ETH_BACKOFFLIMIT_10 0x00000000U |

| #define | ETH_BACKOFFLIMIT_8 0x00000020U |

| #define | ETH_BACKOFFLIMIT_4 0x00000040U |

| #define | ETH_BACKOFFLIMIT_1 0x00000060U |

| #define | ETH_DEFFERRALCHECK_ENABLE 0x00000010U |

| #define | ETH_DEFFERRALCHECK_DISABLE 0x00000000U |

| #define | ETH_RECEIVEALL_ENABLE 0x80000000U |

| #define | ETH_RECEIVEAll_DISABLE 0x00000000U |

| #define | ETH_SOURCEADDRFILTER_NORMAL_ENABLE 0x00000200U |

| #define | ETH_SOURCEADDRFILTER_INVERSE_ENABLE 0x00000300U |

| #define | ETH_SOURCEADDRFILTER_DISABLE 0x00000000U |

| #define | ETH_PASSCONTROLFRAMES_BLOCKALL 0x00000040U |

| #define | ETH_PASSCONTROLFRAMES_FORWARDALL 0x00000080U |

| #define | ETH_PASSCONTROLFRAMES_FORWARDPASSEDADDRFILTER 0x000000C0U |

| #define | ETH_BROADCASTFRAMESRECEPTION_ENABLE 0x00000000U |

| #define | ETH_BROADCASTFRAMESRECEPTION_DISABLE 0x00000020U |

| #define | ETH_DESTINATIONADDRFILTER_NORMAL 0x00000000U |

| #define | ETH_DESTINATIONADDRFILTER_INVERSE 0x00000008U |

| #define | ETH_PROMISCUOUS_MODE_ENABLE 0x00000001U |

| #define | ETH_PROMISCUOUS_MODE_DISABLE 0x00000000U |

| #define | ETH_MULTICASTFRAMESFILTER_PERFECTHASHTABLE 0x00000404U |

| #define | ETH_MULTICASTFRAMESFILTER_HASHTABLE 0x00000004U |

| #define | ETH_MULTICASTFRAMESFILTER_PERFECT 0x00000000U |

| #define | ETH_MULTICASTFRAMESFILTER_NONE 0x00000010U |

| #define | ETH_UNICASTFRAMESFILTER_PERFECTHASHTABLE 0x00000402U |

| #define | ETH_UNICASTFRAMESFILTER_HASHTABLE 0x00000002U |

| #define | ETH_UNICASTFRAMESFILTER_PERFECT 0x00000000U |

| #define | ETH_ZEROQUANTAPAUSE_ENABLE 0x00000000U |

| #define | ETH_ZEROQUANTAPAUSE_DISABLE 0x00000080U |

| #define | ETH_PAUSELOWTHRESHOLD_MINUS4 0x00000000U |

| #define | ETH_PAUSELOWTHRESHOLD_MINUS28 0x00000010U |

| #define | ETH_PAUSELOWTHRESHOLD_MINUS144 0x00000020U |

| #define | ETH_PAUSELOWTHRESHOLD_MINUS256 0x00000030U |

| #define | ETH_UNICASTPAUSEFRAMEDETECT_ENABLE 0x00000008U |

| #define | ETH_UNICASTPAUSEFRAMEDETECT_DISABLE 0x00000000U |

| #define | ETH_RECEIVEFLOWCONTROL_ENABLE 0x00000004U |

| #define | ETH_RECEIVEFLOWCONTROL_DISABLE 0x00000000U |

| #define | ETH_TRANSMITFLOWCONTROL_ENABLE 0x00000002U |

| #define | ETH_TRANSMITFLOWCONTROL_DISABLE 0x00000000U |

| #define | ETH_VLANTAGCOMPARISON_12BIT 0x00010000U |

| #define | ETH_VLANTAGCOMPARISON_16BIT 0x00000000U |

| #define | ETH_MAC_ADDRESS0 0x00000000U |

| #define | ETH_MAC_ADDRESS1 0x00000008U |

| #define | ETH_MAC_ADDRESS2 0x00000010U |

| #define | ETH_MAC_ADDRESS3 0x00000018U |

| #define | ETH_MAC_ADDRESSFILTER_SA 0x00000000U |

| #define | ETH_MAC_ADDRESSFILTER_DA 0x00000008U |

| #define | ETH_MAC_ADDRESSMASK_BYTE6 0x20000000U |

| #define | ETH_MAC_ADDRESSMASK_BYTE5 0x10000000U |

| #define | ETH_MAC_ADDRESSMASK_BYTE4 0x08000000U |

| #define | ETH_MAC_ADDRESSMASK_BYTE3 0x04000000U |

| #define | ETH_MAC_ADDRESSMASK_BYTE2 0x02000000U |

| #define | ETH_MAC_ADDRESSMASK_BYTE1 0x01000000U |

| #define | ETH_DROPTCPIPCHECKSUMERRORFRAME_ENABLE 0x00000000U |

| #define | ETH_DROPTCPIPCHECKSUMERRORFRAME_DISABLE 0x04000000U |

| #define | ETH_RECEIVESTOREFORWARD_ENABLE 0x02000000U |

| #define | ETH_RECEIVESTOREFORWARD_DISABLE 0x00000000U |

| #define | ETH_FLUSHRECEIVEDFRAME_ENABLE 0x00000000U |

| #define | ETH_FLUSHRECEIVEDFRAME_DISABLE 0x01000000U |

| #define | ETH_TRANSMITSTOREFORWARD_ENABLE 0x00200000U |

| #define | ETH_TRANSMITSTOREFORWARD_DISABLE 0x00000000U |

| #define | ETH_TRANSMITTHRESHOLDCONTROL_64BYTES 0x00000000U |

| #define | ETH_TRANSMITTHRESHOLDCONTROL_128BYTES 0x00004000U |

| #define | ETH_TRANSMITTHRESHOLDCONTROL_192BYTES 0x00008000U |

| #define | ETH_TRANSMITTHRESHOLDCONTROL_256BYTES 0x0000C000U |

| #define | ETH_TRANSMITTHRESHOLDCONTROL_40BYTES 0x00010000U |

| #define | ETH_TRANSMITTHRESHOLDCONTROL_32BYTES 0x00014000U |

| #define | ETH_TRANSMITTHRESHOLDCONTROL_24BYTES 0x00018000U |

| #define | ETH_TRANSMITTHRESHOLDCONTROL_16BYTES 0x0001C000U |

| #define | ETH_FORWARDERRORFRAMES_ENABLE 0x00000080U |

| #define | ETH_FORWARDERRORFRAMES_DISABLE 0x00000000U |

| #define | ETH_FORWARDUNDERSIZEDGOODFRAMES_ENABLE 0x00000040U |

| #define | ETH_FORWARDUNDERSIZEDGOODFRAMES_DISABLE 0x00000000U |

| #define | ETH_RECEIVEDTHRESHOLDCONTROL_64BYTES 0x00000000U |

| #define | ETH_RECEIVEDTHRESHOLDCONTROL_32BYTES 0x00000008U |

| #define | ETH_RECEIVEDTHRESHOLDCONTROL_96BYTES 0x00000010U |

| #define | ETH_RECEIVEDTHRESHOLDCONTROL_128BYTES 0x00000018U |

| #define | ETH_SECONDFRAMEOPERARTE_ENABLE 0x00000004U |

| #define | ETH_SECONDFRAMEOPERARTE_DISABLE 0x00000000U |

| #define | ETH_ADDRESSALIGNEDBEATS_ENABLE 0x02000000U |

| #define | ETH_ADDRESSALIGNEDBEATS_DISABLE 0x00000000U |

| #define | ETH_FIXEDBURST_ENABLE 0x00010000U |

| #define | ETH_FIXEDBURST_DISABLE 0x00000000U |

| #define | ETH_RXDMABURSTLENGTH_1BEAT 0x00020000U |

| #define | ETH_RXDMABURSTLENGTH_2BEAT 0x00040000U |

| #define | ETH_RXDMABURSTLENGTH_4BEAT 0x00080000U |

| #define | ETH_RXDMABURSTLENGTH_8BEAT 0x00100000U |

| #define | ETH_RXDMABURSTLENGTH_16BEAT 0x00200000U |

| #define | ETH_RXDMABURSTLENGTH_32BEAT 0x00400000U |

| #define | ETH_RXDMABURSTLENGTH_4XPBL_4BEAT 0x01020000U |

| #define | ETH_RXDMABURSTLENGTH_4XPBL_8BEAT 0x01040000U |

| #define | ETH_RXDMABURSTLENGTH_4XPBL_16BEAT 0x01080000U |

| #define | ETH_RXDMABURSTLENGTH_4XPBL_32BEAT 0x01100000U |

| #define | ETH_RXDMABURSTLENGTH_4XPBL_64BEAT 0x01200000U |

| #define | ETH_RXDMABURSTLENGTH_4XPBL_128BEAT 0x01400000U |

| #define | ETH_TXDMABURSTLENGTH_1BEAT 0x00000100U |

| #define | ETH_TXDMABURSTLENGTH_2BEAT 0x00000200U |

| #define | ETH_TXDMABURSTLENGTH_4BEAT 0x00000400U |

| #define | ETH_TXDMABURSTLENGTH_8BEAT 0x00000800U |

| #define | ETH_TXDMABURSTLENGTH_16BEAT 0x00001000U |

| #define | ETH_TXDMABURSTLENGTH_32BEAT 0x00002000U |

| #define | ETH_TXDMABURSTLENGTH_4XPBL_4BEAT 0x01000100U |

| #define | ETH_TXDMABURSTLENGTH_4XPBL_8BEAT 0x01000200U |

| #define | ETH_TXDMABURSTLENGTH_4XPBL_16BEAT 0x01000400U |

| #define | ETH_TXDMABURSTLENGTH_4XPBL_32BEAT 0x01000800U |

| #define | ETH_TXDMABURSTLENGTH_4XPBL_64BEAT 0x01001000U |

| #define | ETH_TXDMABURSTLENGTH_4XPBL_128BEAT 0x01002000U |

| #define | ETH_DMAENHANCEDDESCRIPTOR_ENABLE 0x00000080U |

| #define | ETH_DMAENHANCEDDESCRIPTOR_DISABLE 0x00000000U |

| #define | ETH_DMAARBITRATION_ROUNDROBIN_RXTX_1_1 0x00000000U |

| #define | ETH_DMAARBITRATION_ROUNDROBIN_RXTX_2_1 0x00004000U |

| #define | ETH_DMAARBITRATION_ROUNDROBIN_RXTX_3_1 0x00008000U |

| #define | ETH_DMAARBITRATION_ROUNDROBIN_RXTX_4_1 0x0000C000U |

| #define | ETH_DMAARBITRATION_RXPRIORTX 0x00000002U |

| #define | ETH_DMATXDESC_LASTSEGMENTS 0x40000000U |

| #define | ETH_DMATXDESC_FIRSTSEGMENT 0x20000000U |

| #define | ETH_DMATXDESC_CHECKSUMBYPASS 0x00000000U |

| #define | ETH_DMATXDESC_CHECKSUMIPV4HEADER 0x00400000U |

| #define | ETH_DMATXDESC_CHECKSUMTCPUDPICMPSEGMENT 0x00800000U |

| #define | ETH_DMATXDESC_CHECKSUMTCPUDPICMPFULL 0x00C00000U |

| #define | ETH_DMARXDESC_BUFFER1 0x00000000U |

| #define | ETH_DMARXDESC_BUFFER2 0x00000001U |

| #define | ETH_PMT_FLAG_WUFFRPR 0x80000000U |

| #define | ETH_PMT_FLAG_WUFR 0x00000040U |

| #define | ETH_PMT_FLAG_MPR 0x00000020U |

| #define | ETH_MMC_IT_TGF 0x00200000U |

| #define | ETH_MMC_IT_TGFMSC 0x00008000U |

| #define | ETH_MMC_IT_TGFSC 0x00004000U |

| #define | ETH_MMC_IT_RGUF 0x10020000U |

| #define | ETH_MMC_IT_RFAE 0x10000040U |

| #define | ETH_MMC_IT_RFCE 0x10000020U |

| #define | ETH_MAC_FLAG_TST 0x00000200U |

| #define | ETH_MAC_FLAG_MMCT 0x00000040U |

| #define | ETH_MAC_FLAG_MMCR 0x00000020U |

| #define | ETH_MAC_FLAG_MMC 0x00000010U |

| #define | ETH_MAC_FLAG_PMT 0x00000008U |

| #define | ETH_DMA_FLAG_TST 0x20000000U |

| #define | ETH_DMA_FLAG_PMT 0x10000000U |

| #define | ETH_DMA_FLAG_MMC 0x08000000U |

| #define | ETH_DMA_FLAG_DATATRANSFERERROR 0x00800000U |

| #define | ETH_DMA_FLAG_READWRITEERROR 0x01000000U |

| #define | ETH_DMA_FLAG_ACCESSERROR 0x02000000U |

| #define | ETH_DMA_FLAG_NIS 0x00010000U |

| #define | ETH_DMA_FLAG_AIS 0x00008000U |

| #define | ETH_DMA_FLAG_ER 0x00004000U |

| #define | ETH_DMA_FLAG_FBE 0x00002000U |

| #define | ETH_DMA_FLAG_ET 0x00000400U |

| #define | ETH_DMA_FLAG_RWT 0x00000200U |

| #define | ETH_DMA_FLAG_RPS 0x00000100U |

| #define | ETH_DMA_FLAG_RBU 0x00000080U |

| #define | ETH_DMA_FLAG_R 0x00000040U |

| #define | ETH_DMA_FLAG_TU 0x00000020U |

| #define | ETH_DMA_FLAG_RO 0x00000010U |

| #define | ETH_DMA_FLAG_TJT 0x00000008U |

| #define | ETH_DMA_FLAG_TBU 0x00000004U |

| #define | ETH_DMA_FLAG_TPS 0x00000002U |

| #define | ETH_DMA_FLAG_T 0x00000001U |

| #define | ETH_MAC_IT_TST 0x00000200U |

| #define | ETH_MAC_IT_MMCT 0x00000040U |

| #define | ETH_MAC_IT_MMCR 0x00000020U |

| #define | ETH_MAC_IT_MMC 0x00000010U |

| #define | ETH_MAC_IT_PMT 0x00000008U |

| #define | ETH_DMA_IT_TST 0x20000000U |

| #define | ETH_DMA_IT_PMT 0x10000000U |

| #define | ETH_DMA_IT_MMC 0x08000000U |

| #define | ETH_DMA_IT_NIS 0x00010000U |

| #define | ETH_DMA_IT_AIS 0x00008000U |

| #define | ETH_DMA_IT_ER 0x00004000U |

| #define | ETH_DMA_IT_FBE 0x00002000U |

| #define | ETH_DMA_IT_ET 0x00000400U |

| #define | ETH_DMA_IT_RWT 0x00000200U |

| #define | ETH_DMA_IT_RPS 0x00000100U |

| #define | ETH_DMA_IT_RBU 0x00000080U |

| #define | ETH_DMA_IT_R 0x00000040U |

| #define | ETH_DMA_IT_TU 0x00000020U |

| #define | ETH_DMA_IT_RO 0x00000010U |

| #define | ETH_DMA_IT_TJT 0x00000008U |

| #define | ETH_DMA_IT_TBU 0x00000004U |

| #define | ETH_DMA_IT_TPS 0x00000002U |

| #define | ETH_DMA_IT_T 0x00000001U |

| #define | ETH_DMA_TRANSMITPROCESS_STOPPED 0x00000000U |

| #define | ETH_DMA_TRANSMITPROCESS_FETCHING 0x00100000U |

| #define | ETH_DMA_TRANSMITPROCESS_WAITING 0x00200000U |

| #define | ETH_DMA_TRANSMITPROCESS_READING 0x00300000U |

| #define | ETH_DMA_TRANSMITPROCESS_SUSPENDED 0x00600000U |

| #define | ETH_DMA_TRANSMITPROCESS_CLOSING 0x00700000U |

| #define | ETH_DMA_RECEIVEPROCESS_STOPPED 0x00000000U |

| #define | ETH_DMA_RECEIVEPROCESS_FETCHING 0x00020000U |

| #define | ETH_DMA_RECEIVEPROCESS_WAITING 0x00060000U |

| #define | ETH_DMA_RECEIVEPROCESS_SUSPENDED 0x00080000U |

| #define | ETH_DMA_RECEIVEPROCESS_CLOSING 0x000A0000U |

| #define | ETH_DMA_RECEIVEPROCESS_QUEUING 0x000E0000U |

| #define | ETH_DMA_OVERFLOW_RXFIFOCOUNTER 0x10000000U |

| #define | ETH_DMA_OVERFLOW_MISSEDFRAMECOUNTER 0x00010000U |

| #define | ETH_EXTI_LINE_WAKEUP 0x00080000U |

| #define | ETH_REG_WRITE_DELAY 0x00000001U |

| #define | ETH_SUCCESS 0U |

| #define | ETH_ERROR 1U |

| #define | ETH_DMATXDESC_COLLISION_COUNTSHIFT 3U |

| #define | ETH_DMATXDESC_BUFFER2_SIZESHIFT 16U |

| #define | ETH_DMARXDESC_FRAME_LENGTHSHIFT 16U |

| #define | ETH_DMARXDESC_BUFFER2_SIZESHIFT 16U |

| #define | ETH_DMARXDESC_FRAMELENGTHSHIFT 16U |

| #define | ETH_MAC_ADDR_HBASE (uint32_t)(ETH_MAC_BASE + 0x40U) /* ETHERNET MAC address high offset */ |

| #define | ETH_MAC_ADDR_LBASE (uint32_t)(ETH_MAC_BASE + 0x44U) /* ETHERNET MAC address low offset */ |

| #define | ETH_MACMIIAR_CR_MASK 0xFFFFFFE3U |

| #define | ETH_MACCR_CLEAR_MASK 0xFF20810FU |

| #define | ETH_MACFCR_CLEAR_MASK 0x0000FF41U |

| #define | ETH_DMAOMR_CLEAR_MASK 0xF8DE3F23U |

| #define | ETH_WAKEUP_REGISTER_LENGTH 8U |

| #define | ETH_DMA_RX_OVERFLOW_MISSEDFRAMES_COUNTERSHIFT 17U |

| #define | MAC_ADDR0 2U |

| #define | MAC_ADDR1 0U |

| #define | MAC_ADDR2 0U |

| #define | MAC_ADDR3 0U |

| #define | MAC_ADDR4 0U |

| #define | MAC_ADDR5 0U |

| #define | ETH_RX_BUF_SIZE ETH_MAX_PACKET_SIZE /* buffer size for receive */ |

| #define | ETH_TX_BUF_SIZE ETH_MAX_PACKET_SIZE /* buffer size for transmit */ |

| #define | ETH_RXBUFNB ((uint32_t)4U) /* 4 Rx buffers of size ETH_RX_BUF_SIZE */ |

| #define | ETH_TXBUFNB ((uint32_t)4U) /* 4 Tx buffers of size ETH_TX_BUF_SIZE */ |

| #define | LAN8742A_PHY_ADDRESS 1U |

| #define | PHY_RESET_DELAY ((uint32_t)0x000000FFU) |

| #define | PHY_CONFIG_DELAY ((uint32_t)0x00000FFFU) |

| #define | PHY_READ_TO ((uint32_t)0x0000FFFFU) |

| #define | PHY_WRITE_TO ((uint32_t)0x0000FFFFU) |

| #define | PHY_BCR ((uint16_t)0x00U) |

| #define | PHY_BSR ((uint16_t)0x01U) |

| #define | PHY_RESET ((uint16_t)0x8000U) |

| #define | PHY_LOOPBACK ((uint16_t)0x4000U) |

| #define | PHY_FULLDUPLEX_100M ((uint16_t)0x2100U) |

| #define | PHY_HALFDUPLEX_100M ((uint16_t)0x2000U) |

| #define | PHY_FULLDUPLEX_10M ((uint16_t)0x0100U) |

| #define | PHY_HALFDUPLEX_10M ((uint16_t)0x0000U) |

| #define | PHY_AUTONEGOTIATION ((uint16_t)0x1000U) |

| #define | PHY_RESTART_AUTONEGOTIATION ((uint16_t)0x0200U) |

| #define | PHY_POWERDOWN ((uint16_t)0x0800U) |

| #define | PHY_ISOLATE ((uint16_t)0x0400U) |

| #define | PHY_AUTONEGO_COMPLETE ((uint16_t)0x0020U) |

| #define | PHY_LINKED_STATUS ((uint16_t)0x0004U) |

| #define | PHY_JABBER_DETECTION ((uint16_t)0x0002U) |

| #define | PHY_SR ((uint16_t)0x1FU) |

| #define | PHY_SPEED_STATUS ((uint16_t)0x0004U) |

| #define | PHY_DUPLEX_STATUS ((uint16_t)0x0010U) |

| #define | PHY_ISFR ((uint16_t)0x001DU) |

| #define | PHY_ISFR_INT4 ((uint16_t)0x001BU) |

| #define | USE_SPI_CRC 0U |

| #define | __ALIGN_END |

| #define | IFNAME0 's' |

| #define | IFNAME1 't' |

| #define | UNUSED(X) (void)X /* To avoid gcc/g++ warnings */ |

| #define | __HAL_ETH_DMA_ENABLE_IT(__HANDLE__, __INTERRUPT__) ((__HANDLE__)->Instance->DMAIER |= (__INTERRUPT__)) |

Typedefs | |

| typedef enum FlagStatus | ITStatus |

Enumerations | |

| enum | LockTypeDef { UNLOCKED = 0x00U , LOCKED = 0x01U } |

| enum | ETH_StateTypeDef { ETH_STATE_RESET = 0x00U , ETH_STATE_READY = 0x01U , ETH_STATE_BUSY = 0x02U , ETH_STATE_BUSY_TX = 0x12U , ETH_STATE_BUSY_RX = 0x22U , ETH_STATE_BUSY_TX_RX = 0x32U , ETH_STATE_BUSY_WR = 0x42U , ETH_STATE_BUSY_RD = 0x82U , ETH_STATE_TIMEOUT = 0x03U , ETH_STATE_ERROR = 0x04U } |

| State structures definition. More... | |

| enum | FlagStatus { RESET = 0U , SET = !RESET } |

Detailed Description

STM32F429 on-chip ETHERNET module class header file.

- Attention

- No special attention requered.

- Copyright

- (C) 2015-2020 ANVILEX LLC $HeadURL: https://192.168.3.4:8443/svn/P004_07/ConOpSys/Targets/STM32F429/ETHERNET_STM32F429.h $

- Revision

- 2262

- Date

- 2020-12-05 07:20:48 +0500 (Sa, 05 Dez 2020)

- Author

- minch