Classes | |

| struct | ETH_InitTypeDef |

| struct | ETH_DMADescTypeDef |

| struct | ETH_DMARxFrameInfos |

| Received Frame Informations structure definition. More... | |

| struct | ETH_MACInitTypeDef |

| ETH MAC Configuration Structure definition. More... | |

| struct | ETH_DMAInitTypeDef |

| ETH DMA Configuration Structure definition. More... | |

| struct | ETH_HandleTypeDef |

| class | TETHERNET_STM32F429 |

| STM32F429 on-chip ETHERNET hardware abstraction layer class. More... | |

Macros | |

| #define | ETH_REG_WRITE_DELAY 0x00000001U |

| #define | ETH_SUCCESS 0U |

| #define | ETH_ERROR 1U |

| #define | ETH_DMATXDESC_COLLISION_COUNTSHIFT 3U |

| #define | ETH_DMATXDESC_BUFFER2_SIZESHIFT 16U |

| #define | ETH_DMARXDESC_FRAME_LENGTHSHIFT 16U |

| #define | ETH_DMARXDESC_BUFFER2_SIZESHIFT 16U |

| #define | ETH_DMARXDESC_FRAMELENGTHSHIFT 16U |

| #define | ETH_MAC_ADDR_HBASE (uint32_t)(ETH_MAC_BASE + 0x40U) /* ETHERNET MAC address high offset */ |

| #define | ETH_MAC_ADDR_LBASE (uint32_t)(ETH_MAC_BASE + 0x44U) /* ETHERNET MAC address low offset */ |

| #define | ETH_MACMIIAR_CR_MASK 0xFFFFFFE3U |

| #define | ETH_MACCR_CLEAR_MASK 0xFF20810FU |

| #define | ETH_MACFCR_CLEAR_MASK 0x0000FF41U |

| #define | ETH_DMAOMR_CLEAR_MASK 0xF8DE3F23U |

| #define | ETH_WAKEUP_REGISTER_LENGTH 8U |

| #define | ETH_DMA_RX_OVERFLOW_MISSEDFRAMES_COUNTERSHIFT 17U |

| #define | MAC_ADDR0 2U |

| #define | MAC_ADDR1 0U |

| #define | MAC_ADDR2 0U |

| #define | MAC_ADDR3 0U |

| #define | MAC_ADDR4 0U |

| #define | MAC_ADDR5 0U |

| #define | ETH_RX_BUF_SIZE ETH_MAX_PACKET_SIZE /* buffer size for receive */ |

| #define | ETH_TX_BUF_SIZE ETH_MAX_PACKET_SIZE /* buffer size for transmit */ |

| #define | ETH_RXBUFNB ((uint32_t)4U) /* 4 Rx buffers of size ETH_RX_BUF_SIZE */ |

| #define | ETH_TXBUFNB ((uint32_t)4U) /* 4 Tx buffers of size ETH_TX_BUF_SIZE */ |

| #define | LAN8742A_PHY_ADDRESS 1U |

| #define | PHY_RESET_DELAY ((uint32_t)0x000000FFU) |

| #define | PHY_CONFIG_DELAY ((uint32_t)0x00000FFFU) |

| #define | PHY_READ_TO ((uint32_t)0x0000FFFFU) |

| #define | PHY_WRITE_TO ((uint32_t)0x0000FFFFU) |

| #define | PHY_BCR ((uint16_t)0x00U) |

| #define | PHY_BSR ((uint16_t)0x01U) |

| #define | PHY_RESET ((uint16_t)0x8000U) |

| #define | PHY_LOOPBACK ((uint16_t)0x4000U) |

| #define | PHY_FULLDUPLEX_100M ((uint16_t)0x2100U) |

| #define | PHY_HALFDUPLEX_100M ((uint16_t)0x2000U) |

| #define | PHY_FULLDUPLEX_10M ((uint16_t)0x0100U) |

| #define | PHY_HALFDUPLEX_10M ((uint16_t)0x0000U) |

| #define | PHY_AUTONEGOTIATION ((uint16_t)0x1000U) |

| #define | PHY_RESTART_AUTONEGOTIATION ((uint16_t)0x0200U) |

| #define | PHY_POWERDOWN ((uint16_t)0x0800U) |

| #define | PHY_ISOLATE ((uint16_t)0x0400U) |

| #define | PHY_AUTONEGO_COMPLETE ((uint16_t)0x0020U) |

| #define | PHY_LINKED_STATUS ((uint16_t)0x0004U) |

| #define | PHY_JABBER_DETECTION ((uint16_t)0x0002U) |

| #define | PHY_SR ((uint16_t)0x1FU) |

| #define | PHY_SPEED_STATUS ((uint16_t)0x0004U) |

| #define | PHY_DUPLEX_STATUS ((uint16_t)0x0010U) |

| #define | PHY_ISFR ((uint16_t)0x001DU) |

| #define | PHY_ISFR_INT4 ((uint16_t)0x001BU) |

| #define | USE_SPI_CRC 0U |

| #define | __ALIGN_END |

| #define | IFNAME0 's' |

| #define | IFNAME1 't' |

| #define | UNUSED(X) (void)X /* To avoid gcc/g++ warnings */ |

| #define | __HAL_ETH_DMA_ENABLE_IT(__HANDLE__, __INTERRUPT__) ((__HANDLE__)->Instance->DMAIER |= (__INTERRUPT__)) |

Typedefs | |

| typedef enum FlagStatus | ITStatus |

Enumerations | |

| enum | LockTypeDef { UNLOCKED = 0x00U , LOCKED = 0x01U } |

| enum | ETH_StateTypeDef { ETH_STATE_RESET = 0x00U , ETH_STATE_READY = 0x01U , ETH_STATE_BUSY = 0x02U , ETH_STATE_BUSY_TX = 0x12U , ETH_STATE_BUSY_RX = 0x22U , ETH_STATE_BUSY_TX_RX = 0x32U , ETH_STATE_BUSY_WR = 0x42U , ETH_STATE_BUSY_RD = 0x82U , ETH_STATE_TIMEOUT = 0x03U , ETH_STATE_ERROR = 0x04U } |

| State structures definition. More... | |

| enum | FlagStatus { RESET = 0U , SET = !RESET } |

Detailed Description

Macro Definition Documentation

◆ __ALIGN_END

| #define __ALIGN_END |

◆ __HAL_ETH_DMA_ENABLE_IT

| #define __HAL_ETH_DMA_ENABLE_IT | ( | __HANDLE__, | |

| __INTERRUPT__ | |||

| ) | ((__HANDLE__)->Instance->DMAIER |= (__INTERRUPT__)) |

◆ ETH_DMA_RX_OVERFLOW_MISSEDFRAMES_COUNTERSHIFT

| #define ETH_DMA_RX_OVERFLOW_MISSEDFRAMES_COUNTERSHIFT 17U |

◆ ETH_DMAOMR_CLEAR_MASK

| #define ETH_DMAOMR_CLEAR_MASK 0xF8DE3F23U |

◆ ETH_DMARXDESC_BUFFER2_SIZESHIFT

| #define ETH_DMARXDESC_BUFFER2_SIZESHIFT 16U |

◆ ETH_DMARXDESC_FRAME_LENGTHSHIFT

| #define ETH_DMARXDESC_FRAME_LENGTHSHIFT 16U |

◆ ETH_DMARXDESC_FRAMELENGTHSHIFT

| #define ETH_DMARXDESC_FRAMELENGTHSHIFT 16U |

◆ ETH_DMATXDESC_BUFFER2_SIZESHIFT

| #define ETH_DMATXDESC_BUFFER2_SIZESHIFT 16U |

◆ ETH_DMATXDESC_COLLISION_COUNTSHIFT

| #define ETH_DMATXDESC_COLLISION_COUNTSHIFT 3U |

◆ ETH_ERROR

| #define ETH_ERROR 1U |

◆ ETH_MAC_ADDR_HBASE

| #define ETH_MAC_ADDR_HBASE (uint32_t)(ETH_MAC_BASE + 0x40U) /* ETHERNET MAC address high offset */ |

◆ ETH_MAC_ADDR_LBASE

| #define ETH_MAC_ADDR_LBASE (uint32_t)(ETH_MAC_BASE + 0x44U) /* ETHERNET MAC address low offset */ |

◆ ETH_MACCR_CLEAR_MASK

| #define ETH_MACCR_CLEAR_MASK 0xFF20810FU |

◆ ETH_MACFCR_CLEAR_MASK

| #define ETH_MACFCR_CLEAR_MASK 0x0000FF41U |

◆ ETH_MACMIIAR_CR_MASK

| #define ETH_MACMIIAR_CR_MASK 0xFFFFFFE3U |

◆ ETH_REG_WRITE_DELAY

| #define ETH_REG_WRITE_DELAY 0x00000001U |

◆ ETH_RX_BUF_SIZE

| #define ETH_RX_BUF_SIZE ETH_MAX_PACKET_SIZE /* buffer size for receive */ |

◆ ETH_RXBUFNB

| #define ETH_RXBUFNB ((uint32_t)4U) /* 4 Rx buffers of size ETH_RX_BUF_SIZE */ |

◆ ETH_SUCCESS

| #define ETH_SUCCESS 0U |

◆ ETH_TX_BUF_SIZE

| #define ETH_TX_BUF_SIZE ETH_MAX_PACKET_SIZE /* buffer size for transmit */ |

◆ ETH_TXBUFNB

| #define ETH_TXBUFNB ((uint32_t)4U) /* 4 Tx buffers of size ETH_TX_BUF_SIZE */ |

◆ ETH_WAKEUP_REGISTER_LENGTH

| #define ETH_WAKEUP_REGISTER_LENGTH 8U |

◆ IFNAME0

| #define IFNAME0 's' |

◆ IFNAME1

| #define IFNAME1 't' |

◆ LAN8742A_PHY_ADDRESS

| #define LAN8742A_PHY_ADDRESS 1U |

◆ MAC_ADDR0

| #define MAC_ADDR0 2U |

◆ MAC_ADDR1

| #define MAC_ADDR1 0U |

◆ MAC_ADDR2

| #define MAC_ADDR2 0U |

◆ MAC_ADDR3

| #define MAC_ADDR3 0U |

◆ MAC_ADDR4

| #define MAC_ADDR4 0U |

◆ MAC_ADDR5

| #define MAC_ADDR5 0U |

◆ PHY_AUTONEGO_COMPLETE

| #define PHY_AUTONEGO_COMPLETE ((uint16_t)0x0020U) |

Auto-Negotiation process completed

◆ PHY_AUTONEGOTIATION

| #define PHY_AUTONEGOTIATION ((uint16_t)0x1000U) |

Enable auto-negotiation function

◆ PHY_BCR

| #define PHY_BCR ((uint16_t)0x00U) |

Transceiver Basic Control Register

◆ PHY_BSR

| #define PHY_BSR ((uint16_t)0x01U) |

Transceiver Basic Status Register

◆ PHY_CONFIG_DELAY

| #define PHY_CONFIG_DELAY ((uint32_t)0x00000FFFU) |

◆ PHY_DUPLEX_STATUS

| #define PHY_DUPLEX_STATUS ((uint16_t)0x0010U) |

PHY Duplex mask

◆ PHY_FULLDUPLEX_100M

| #define PHY_FULLDUPLEX_100M ((uint16_t)0x2100U) |

Set the full-duplex mode at 100 Mb/s

◆ PHY_FULLDUPLEX_10M

| #define PHY_FULLDUPLEX_10M ((uint16_t)0x0100U) |

Set the full-duplex mode at 10 Mb/s

◆ PHY_HALFDUPLEX_100M

| #define PHY_HALFDUPLEX_100M ((uint16_t)0x2000U) |

Set the half-duplex mode at 100 Mb/s

◆ PHY_HALFDUPLEX_10M

| #define PHY_HALFDUPLEX_10M ((uint16_t)0x0000U) |

Set the half-duplex mode at 10 Mb/s

◆ PHY_ISFR

| #define PHY_ISFR ((uint16_t)0x001DU) |

PHY Interrupt Source Flag register Offset

◆ PHY_ISFR_INT4

| #define PHY_ISFR_INT4 ((uint16_t)0x001BU) |

PHY Link down inturrupt

◆ PHY_ISOLATE

| #define PHY_ISOLATE ((uint16_t)0x0400U) |

Isolate PHY from MII

◆ PHY_JABBER_DETECTION

| #define PHY_JABBER_DETECTION ((uint16_t)0x0002U) |

Jabber condition detected

◆ PHY_LINKED_STATUS

| #define PHY_LINKED_STATUS ((uint16_t)0x0004U) |

Valid link established

◆ PHY_LOOPBACK

| #define PHY_LOOPBACK ((uint16_t)0x4000U) |

Select loop-back mode

◆ PHY_POWERDOWN

| #define PHY_POWERDOWN ((uint16_t)0x0800U) |

Select the power down mode

◆ PHY_READ_TO

| #define PHY_READ_TO ((uint32_t)0x0000FFFFU) |

◆ PHY_RESET

| #define PHY_RESET ((uint16_t)0x8000U) |

PHY Reset

◆ PHY_RESET_DELAY

| #define PHY_RESET_DELAY ((uint32_t)0x000000FFU) |

◆ PHY_RESTART_AUTONEGOTIATION

| #define PHY_RESTART_AUTONEGOTIATION ((uint16_t)0x0200U) |

Restart auto-negotiation function

◆ PHY_SPEED_STATUS

| #define PHY_SPEED_STATUS ((uint16_t)0x0004U) |

PHY Speed mask

◆ PHY_SR

| #define PHY_SR ((uint16_t)0x1FU) |

PHY status register Offset

◆ PHY_WRITE_TO

| #define PHY_WRITE_TO ((uint32_t)0x0000FFFFU) |

◆ UNUSED

◆ USE_SPI_CRC

| #define USE_SPI_CRC 0U |

Typedef Documentation

◆ ITStatus

| typedef enum FlagStatus ITStatus |

Enumeration Type Documentation

◆ ETH_StateTypeDef

| enum ETH_StateTypeDef |

State structures definition.

◆ FlagStatus

| enum FlagStatus |

◆ LockTypeDef

| enum LockTypeDef |

Function Documentation

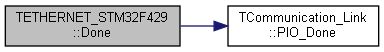

◆ Done()

| VOID TETHERNET_STM32F429::Done | ( | ) |

Object finalisation method.

- Note

- None

- Returns

- None

- Override

- Not allowed

- Attention

- None

References TCommunication_Link::PIO_Done().

◆ ETH_ConfigDMA()

| BOOL ETH_ConfigDMA | ( | ETH_HandleTypeDef * | heth, |

| ETH_MACInitTypeDef * | macconf | ||

| ) |

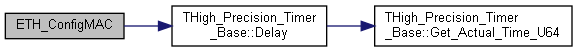

◆ ETH_ConfigMAC()

| BOOL ETH_ConfigMAC | ( | ETH_HandleTypeDef * | heth, |

| ETH_MACInitTypeDef * | macconf | ||

| ) |

Set ETH MAC Configuration.

- Parameters

-

heth pointer to a ETH_HandleTypeDef structure that contains the configuration information for ETHERNET module macconf MAC Configuration structure

- Return values

-

HAL status

References ETH_MACInitTypeDef::AutomaticPadCRCStrip, ETH_MACInitTypeDef::BackOffLimit, ETH_MACInitTypeDef::BroadcastFramesReception, ETH_MACInitTypeDef::CarrierSense, ETH_MACInitTypeDef::ChecksumOffload, ETH_MACInitTypeDef::DeferralCheck, THigh_Precision_Timer_Base::Delay(), ETH_MACInitTypeDef::DestinationAddrFilter, ETH_InitTypeDef::DuplexMode, ETH_MACCR_CLEAR_MASK, ETH_MACFCR_CLEAR_MASK, ETH_STATE_BUSY, ETH_STATE_READY, ETH_MACInitTypeDef::HashTableHigh, ETH_MACInitTypeDef::HashTableLow, heth, ETH_HandleTypeDef::Init, ETH_HandleTypeDef::Instance, ETH_MACInitTypeDef::InterFrameGap, ETH_MACInitTypeDef::Jabber, ETH_HandleTypeDef::Lock, LOCKED, ETH_MACInitTypeDef::LoopbackMode, ETH_MACInitTypeDef::MulticastFramesFilter, NULL, object_Delay_Timer, ETH_MACInitTypeDef::PassControlFrames, ETH_MACInitTypeDef::PauseLowThreshold, ETH_MACInitTypeDef::PauseTime, ETH_MACInitTypeDef::PromiscuousMode, ETH_MACInitTypeDef::ReceiveAll, ETH_MACInitTypeDef::ReceiveFlowControl, ETH_MACInitTypeDef::ReceiveOwn, ETH_MACInitTypeDef::RetryTransmission, ETH_MACInitTypeDef::SourceAddrFilter, ETH_InitTypeDef::Speed, ETH_HandleTypeDef::State, ETH_MACInitTypeDef::TransmitFlowControl, ETH_MACInitTypeDef::UnicastFramesFilter, ETH_MACInitTypeDef::UnicastPauseFrameDetect, UNLOCKED, ETH_MACInitTypeDef::VLANTagComparison, ETH_MACInitTypeDef::VLANTagIdentifier, ETH_MACInitTypeDef::Watchdog, and ETH_MACInitTypeDef::ZeroQuantaPause.

Referenced by ethernetif_update_config().

◆ ETH_DMAReceptionDisable()

|

static |

◆ ETH_DMAReceptionEnable()

|

static |

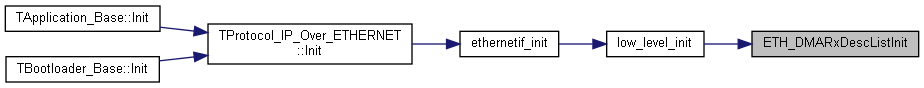

◆ ETH_DMARxDescListInit()

| BOOL ETH_DMARxDescListInit | ( | ETH_HandleTypeDef * | heth, |

| ETH_DMADescTypeDef * | DMARxDescTab, | ||

| uint8_t * | RxBuff, | ||

| uint32_t | RxBuffCount | ||

| ) |

initialises the DMA Rx descriptors in chain mode.

- Parameters

-

heth pointer to a ETH_HandleTypeDef structure that contains the configuration information for ETHERNET module

DMARxDescTab Pointer to the first Rx desc list RxBuff Pointer to the first RxBuffer list RxBuffCount Number of the used Rx desc in the list

- Return values

-

HAL status

References ETH_DMADescTypeDef::Buffer1Addr, ETH_DMADescTypeDef::Buffer2NextDescAddr, ETH_DMADescTypeDef::ControlBufferSize, ETH_DMARXDESC_DIC, ETH_DMARXDESC_OWN, ETH_DMARXDESC_RCH, ETH_RX_BUF_SIZE, ETH_RXINTERRUPT_MODE, ETH_STATE_BUSY, ETH_STATE_READY, heth, ETH_HandleTypeDef::Init, ETH_HandleTypeDef::Instance, ETH_HandleTypeDef::Lock, LOCKED, ETH_HandleTypeDef::RxDesc, ETH_HandleTypeDef::State, ETH_DMADescTypeDef::Status, and UNLOCKED.

Referenced by low_level_init().

◆ ETH_DMATransmissionDisable()

|

static |

◆ ETH_DMATransmissionEnable()

|

static |

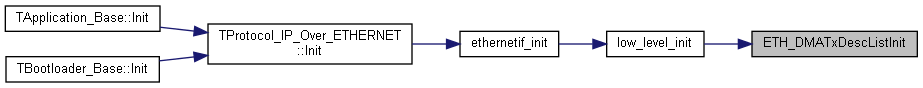

◆ ETH_DMATxDescListInit()

| BOOL ETH_DMATxDescListInit | ( | ETH_HandleTypeDef * | heth, |

| ETH_DMADescTypeDef * | DMATxDescTab, | ||

| uint8_t * | TxBuff, | ||

| uint32_t | TxBuffCount | ||

| ) |

initialises the DMA Tx descriptors in chain mode.

- Parameters

-

heth pointer to a ETH_HandleTypeDef structure that contains the configuration information for ETHERNET module

DMATxDescTab Pointer to the first Tx desc list TxBuff Pointer to the first TxBuffer list TxBuffCount Number of the used Tx desc in the list

- Return values

-

HAL status

References ETH_DMADescTypeDef::Buffer1Addr, ETH_DMADescTypeDef::Buffer2NextDescAddr, ETH_CHECKSUM_BY_HARDWARE, ETH_DMATXDESC_CHECKSUMTCPUDPICMPFULL, ETH_DMATXDESC_TCH, ETH_STATE_BUSY, ETH_STATE_READY, ETH_TX_BUF_SIZE, heth, ETH_HandleTypeDef::Init, ETH_HandleTypeDef::Instance, ETH_HandleTypeDef::Lock, LOCKED, ETH_HandleTypeDef::State, ETH_DMADescTypeDef::Status, ETH_HandleTypeDef::TxDesc, and UNLOCKED.

Referenced by low_level_init().

◆ ETH_FlushTransmitFIFO()

|

static |

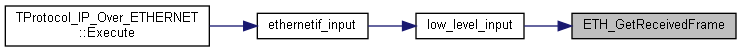

◆ ETH_GetReceivedFrame()

| BOOL ETH_GetReceivedFrame | ( | ETH_HandleTypeDef * | heth | ) |

**

Checks for received frames.

- Parameters

-

heth pointer to a ETH_HandleTypeDef structure that contains the configuration information for ETHERNET module

- Return values

-

HAL status

References ETH_DMARxFrameInfos::buffer, ETH_DMADescTypeDef::Buffer2NextDescAddr, ETH_DMARXDESC_FL, ETH_DMARXDESC_FRAMELENGTHSHIFT, ETH_DMARXDESC_FS, ETH_DMARXDESC_LS, ETH_DMARXDESC_OWN, ETH_STATE_BUSY, ETH_STATE_READY, heth, ETH_DMARxFrameInfos::length, ETH_HandleTypeDef::Lock, LOCKED, ETH_DMARxFrameInfos::LSRxDesc, NULL, RESET, ETH_HandleTypeDef::RxDesc, ETH_HandleTypeDef::RxFrameInfos, ETH_HandleTypeDef::State, ETH_DMADescTypeDef::Status, and UNLOCKED.

Referenced by low_level_input().

◆ ETH_MACAddressConfig()

|

static |

◆ ETH_MACDMAConfig()

|

static |

◆ ETH_MACReceptionDisable()

|

static |

◆ ETH_MACReceptionEnable()

|

static |

◆ ETH_MACTransmissionDisable()

|

static |

◆ ETH_MACTransmissionEnable()

|

static |

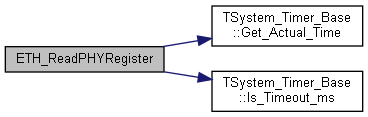

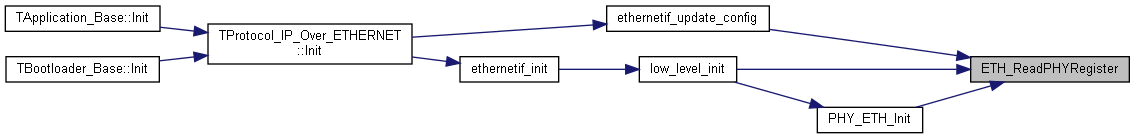

◆ ETH_ReadPHYRegister()

| BOOL ETH_ReadPHYRegister | ( | ETH_HandleTypeDef * | heth, |

| uint16_t | PHYReg, | ||

| uint32_t * | RegValue | ||

| ) |

References ETH_MACMIIAR_CR_MASK, ETH_STATE_BUSY_RD, ETH_STATE_READY, TSystem_Timer_Base::Get_Actual_Time(), heth, ETH_HandleTypeDef::Init, ETH_HandleTypeDef::Instance, TSystem_Timer_Base::Is_Timeout_ms(), ETH_HandleTypeDef::Lock, object_System_Timer, ETH_InitTypeDef::PhyAddress, ETH_HandleTypeDef::State, true, and UNLOCKED.

Referenced by ethernetif_update_config(), low_level_init(), and PHY_ETH_Init().

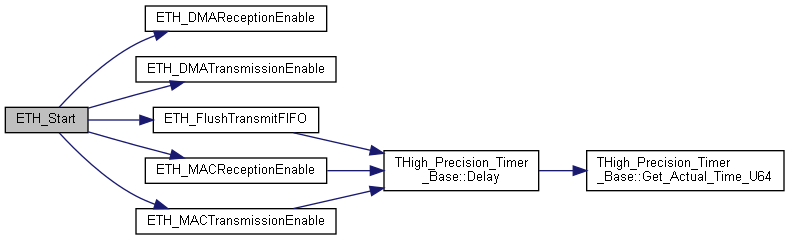

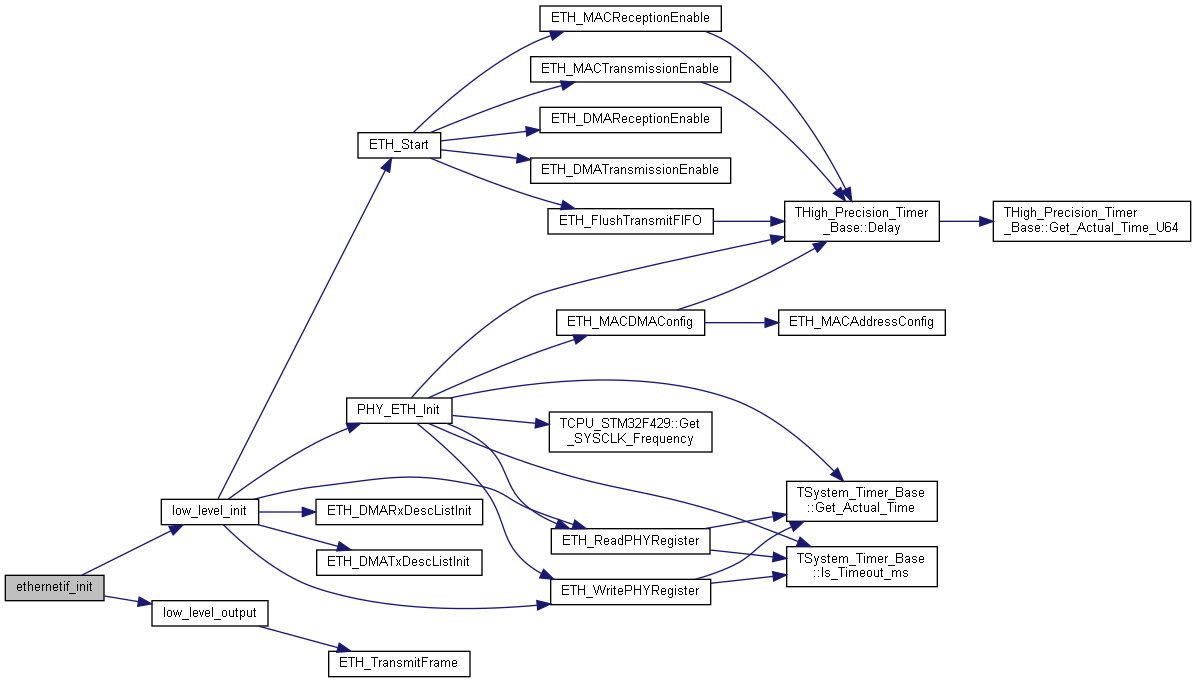

◆ ETH_Start()

| BOOL ETH_Start | ( | ETH_HandleTypeDef * | heth | ) |

Enables Ethernet MAC and DMA reception/transmission.

- Parameters

-

heth pointer to a ETH_HandleTypeDef structure that contains the configuration information for ETHERNET module

- Return values

-

HAL status

References ETH_DMAReceptionEnable(), ETH_DMATransmissionEnable(), ETH_FlushTransmitFIFO(), ETH_MACReceptionEnable(), ETH_MACTransmissionEnable(), ETH_STATE_BUSY, ETH_STATE_READY, heth, ETH_HandleTypeDef::Lock, LOCKED, ETH_HandleTypeDef::State, and UNLOCKED.

Referenced by ethernetif_update_config(), and low_level_init().

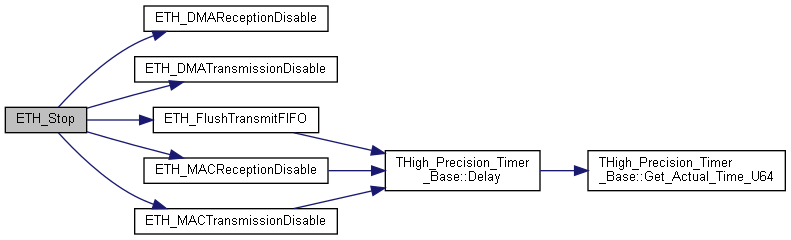

◆ ETH_Stop()

| BOOL ETH_Stop | ( | ETH_HandleTypeDef * | heth | ) |

Stop Ethernet MAC and DMA reception/transmission.

- Parameters

-

heth pointer to a ETH_HandleTypeDef structure that contains the configuration information for ETHERNET module

- Return values

-

HAL status

References ETH_DMAReceptionDisable(), ETH_DMATransmissionDisable(), ETH_FlushTransmitFIFO(), ETH_MACReceptionDisable(), ETH_MACTransmissionDisable(), ETH_STATE_BUSY, ETH_STATE_READY, heth, ETH_HandleTypeDef::Lock, LOCKED, ETH_HandleTypeDef::State, and UNLOCKED.

Referenced by ethernetif_update_config().

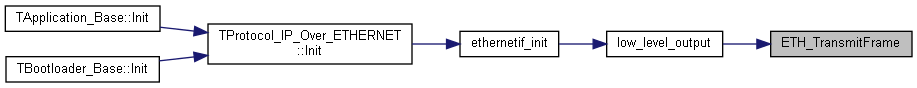

◆ ETH_TransmitFrame()

| BOOL ETH_TransmitFrame | ( | ETH_HandleTypeDef * | heth, |

| uint32_t | FrameLength | ||

| ) |

References ETH_DMADescTypeDef::Buffer2NextDescAddr, ETH_DMADescTypeDef::ControlBufferSize, ETH_DMATXDESC_FS, ETH_DMATXDESC_LS, ETH_DMATXDESC_OWN, ETH_DMATXDESC_TBS1, ETH_STATE_BUSY, ETH_STATE_BUSY_TX, ETH_STATE_READY, ETH_TX_BUF_SIZE, heth, ETH_HandleTypeDef::Instance, ETH_HandleTypeDef::Lock, LOCKED, RESET, ETH_HandleTypeDef::State, ETH_DMADescTypeDef::Status, ETH_HandleTypeDef::TxDesc, and UNLOCKED.

Referenced by low_level_output().

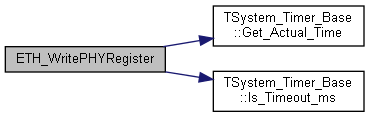

◆ ETH_WritePHYRegister()

| BOOL ETH_WritePHYRegister | ( | ETH_HandleTypeDef * | heth, |

| uint16_t | PHYReg, | ||

| uint32_t | RegValue | ||

| ) |

References ETH_MACMIIAR_CR_MASK, ETH_STATE_BUSY_WR, ETH_STATE_READY, TSystem_Timer_Base::Get_Actual_Time(), heth, ETH_HandleTypeDef::Init, ETH_HandleTypeDef::Instance, TSystem_Timer_Base::Is_Timeout_ms(), ETH_HandleTypeDef::Lock, object_System_Timer, ETH_InitTypeDef::PhyAddress, ETH_HandleTypeDef::State, true, and UNLOCKED.

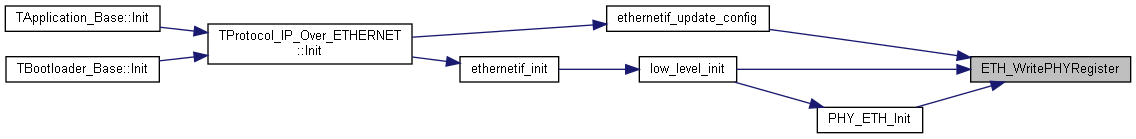

Referenced by ethernetif_update_config(), low_level_init(), and PHY_ETH_Init().

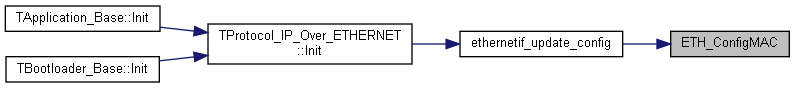

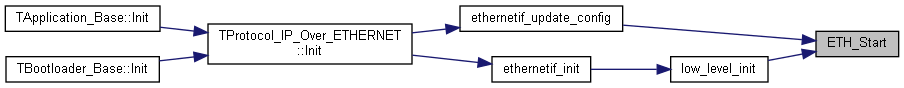

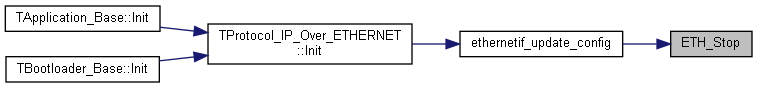

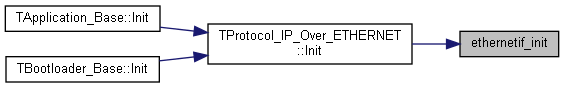

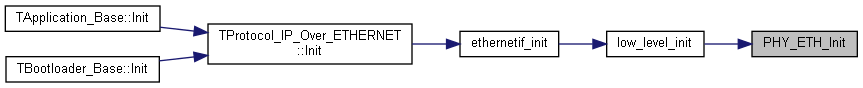

◆ ethernetif_init()

References ERR_OK, IFNAME0, IFNAME1, netif::linkoutput, low_level_init(), low_level_output(), LWIP_ASSERT, netif::name, and NULL.

Referenced by TProtocol_IP_Over_ETHERNET::Init().

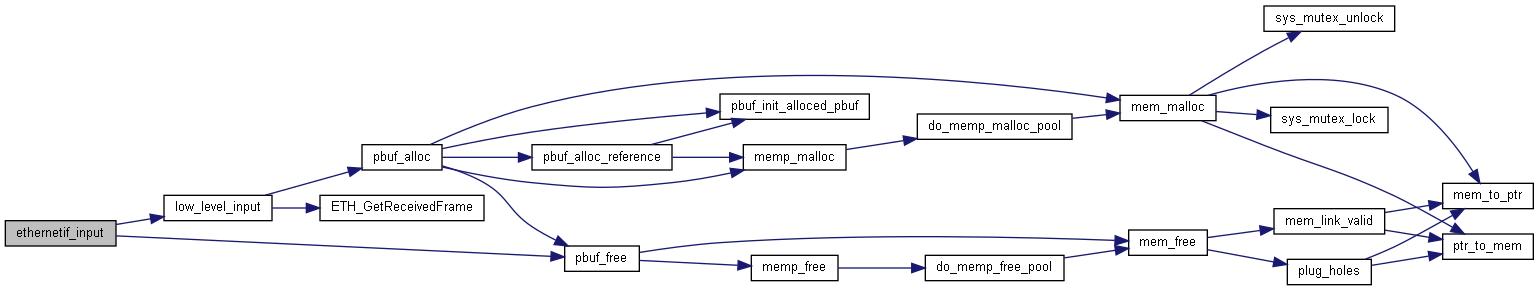

◆ ethernetif_input()

| void ethernetif_input | ( | struct netif * | netif | ) |

This function should be called when a packet is ready to be read from the interface. It uses the function low_level_input() that should handle the actual reception of bytes from the network interface. Then the type of the received packet is determined and the appropriate input function is called.

- Parameters

-

netif the lwip network interface structure for this ethernetif

References ERR_OK, netif::input, low_level_input(), LWIP_DEBUGF, NETIF_DEBUG, NULL, and pbuf_free().

Referenced by TProtocol_IP_Over_ETHERNET::Execute().

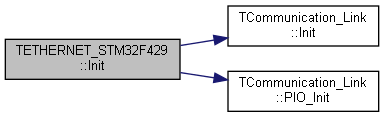

◆ Init()

| VOID TETHERNET_STM32F429::Init | ( | ) |

Object initialisation method.

- Note

- None

- Returns

- None

- Override

- Not allowed

- Attention

- None

References TCommunication_Link::Init(), and TCommunication_Link::PIO_Init().

◆ Interrupt()

| VOID TETHERNET_STM32F429::Interrupt | ( | ) |

Interrupt service method.

- Note

- None

- Returns

- None

- Override

- Not allowed / Requered / Optional

- Attention

- None

◆ Interrupt_Disable()

| VOID TETHERNET_STM32F429::Interrupt_Disable | ( | ) |

Disable interrupt method.

- Note

- None

- Returns

- None

- Override

- Not allowed / Requered / Optional

- Attention

- None

◆ Interrupt_Enable()

Enable interrupt method.

- Note

- None

- Parameters

-

[in] u32_Priority - Interrupt priority

- Returns

- None

- Override

- Not allowed / Requered / Optional

- Attention

- None

◆ low_level_init()

◆ low_level_input()

◆ low_level_output()

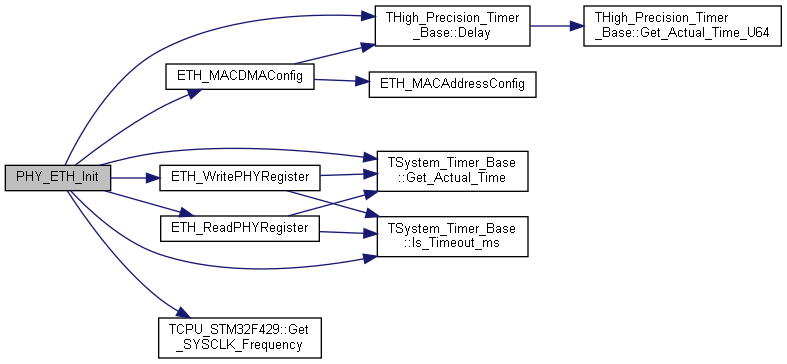

◆ PHY_ETH_Init()

| BOOL PHY_ETH_Init | ( | ETH_HandleTypeDef * | heth | ) |

References THigh_Precision_Timer_Base::Delay(), ETH_AUTONEGOTIATION_DISABLE, ETH_ERROR, ETH_MACDMAConfig(), ETH_MACMIIAR_CR_MASK, ETH_MODE_FULLDUPLEX, ETH_MODE_HALFDUPLEX, ETH_ReadPHYRegister(), ETH_SPEED_100M, ETH_SPEED_10M, ETH_STATE_READY, ETH_STATE_RESET, ETH_STATE_TIMEOUT, ETH_SUCCESS, ETH_WritePHYRegister(), false, TSystem_Timer_Base::Get_Actual_Time(), TCPU_STM32F429::Get_SYSCLK_Frequency(), heth, ETH_HandleTypeDef::Init, ETH_HandleTypeDef::Instance, TSystem_Timer_Base::Is_Timeout_ms(), ETH_HandleTypeDef::Lock, ETH_InitTypeDef::MediaInterface, NULL, object_Delay_Timer, object_System_CPU, object_System_Timer, PHY_AUTONEGO_COMPLETE, PHY_AUTONEGOTIATION, PHY_BCR, PHY_BSR, PHY_DUPLEX_STATUS, PHY_LINKED_STATUS, PHY_RESET, PHY_SPEED_STATUS, PHY_SR, RESET, ETH_HandleTypeDef::State, true, and UNLOCKED.

Referenced by low_level_init().

◆ Start_TX_Operation()

| VOID TETHERNET_STM32F429::Start_TX_Operation | ( | ) |

Start RX operation.

- Note

- Calling this method enables RX operation of the ETHERNET.

- Returns

- None

- Override

- Not allowed

- Attention

- None

Stop RX operation.

- Note

- Calling this method enables RX operation of the ETHERNET.

- Returns

- None

- Override

- Not allowed

- Attention

- None

Start TX operation.

- Note

- Calling this method enables RX operation of the ETHERNET.

- Returns

- None

- Override

- Not allowed

- Attention

- None

◆ Stop_TX_Operation()

| VOID TETHERNET_STM32F429::Stop_TX_Operation | ( | ) |

Stop TX operation.

- Note

- Calling this method enables RX operation of the ETHERNET.

- Returns

- None

- Override

- Not allowed

- Attention

- None

Variable Documentation

◆ AddressAlignedBeats

| uint32_t ETH_DMAInitTypeDef::AddressAlignedBeats |

Enables or disables the Address Aligned Beats. This parameter can be a value of ETH Address Aligned Beats

Referenced by ETH_MACDMAConfig().

◆ AutomaticPadCRCStrip

| uint32_t ETH_MACInitTypeDef::AutomaticPadCRCStrip |

Selects or not the Automatic MAC Pad/CRC Stripping. This parameter can be a value of ETH Automatic Pad CRC Strip

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ AutoNegotiation

| uint32_t ETH_InitTypeDef::AutoNegotiation |

Selects or not the AutoNegotiation mode for the external PHY The AutoNegotiation allows an automatic setting of the Speed (10/100Mbps) and the mode (half/full-duplex). This parameter can be a value of ETH AutoNegotiation

Referenced by ethernetif_update_config(), and low_level_init().

◆ BackOffLimit

| uint32_t ETH_MACInitTypeDef::BackOffLimit |

Selects the BackOff limit value. This parameter can be a value of ETH Back Off Limit

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ BroadcastFramesReception

| uint32_t ETH_MACInitTypeDef::BroadcastFramesReception |

Selects or not the reception of Broadcast Frames. This parameter can be a value of ETH Broadcast Frames Reception

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ buffer

| uint32_t ETH_DMARxFrameInfos::buffer |

Frame buffer

Referenced by ETH_GetReceivedFrame(), and low_level_input().

◆ Buffer1Addr

| uint32_t ETH_DMADescTypeDef::Buffer1Addr |

Buffer1 address pointer

Referenced by ETH_DMARxDescListInit(), ETH_DMATxDescListInit(), HAL_ETH_DMATxDescListInit(), and low_level_output().

◆ Buffer2NextDescAddr

| uint32_t ETH_DMADescTypeDef::Buffer2NextDescAddr |

Buffer2 or next descriptor address pointer Enhanced ETHERNET DMA PTP Descriptors

Referenced by ETH_DMARxDescListInit(), ETH_DMATxDescListInit(), ETH_GetReceivedFrame(), ETH_TransmitFrame(), and HAL_ETH_DMATxDescListInit().

◆ CarrierSense

| uint32_t ETH_MACInitTypeDef::CarrierSense |

Selects or not the Carrier Sense. This parameter can be a value of ETH Carrier Sense

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ ChecksumMode

| uint32_t ETH_InitTypeDef::ChecksumMode |

Selects if the checksum is check by hardware or by software. This parameter can be a value of ETH Checksum Mode

Referenced by ETH_MACDMAConfig(), and low_level_init().

◆ ChecksumOffload

| uint32_t ETH_MACInitTypeDef::ChecksumOffload |

Selects or not the IPv4 checksum checking for received frame payloads' TCP/UDP/ICMP headers. This parameter can be a value of ETH Checksum Offload

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ ControlBufferSize

| uint32_t ETH_DMADescTypeDef::ControlBufferSize |

Control and Buffer1, Buffer2 lengths

Referenced by ETH_DMARxDescListInit(), and ETH_TransmitFrame().

◆ DeferralCheck

| uint32_t ETH_MACInitTypeDef::DeferralCheck |

Selects or not the deferral check function (Half-Duplex mode). This parameter can be a value of ETH Deferral Check

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ DescriptorSkipLength

| uint32_t ETH_DMAInitTypeDef::DescriptorSkipLength |

Specifies the number of word to skip between two unchained descriptors (Ring mode) This parameter must be a number between Min_Data = 0 and Max_Data = 32

Referenced by ETH_MACDMAConfig().

◆ DestinationAddrFilter

| uint32_t ETH_MACInitTypeDef::DestinationAddrFilter |

Sets the destination filter mode for both unicast and multicast frames. This parameter can be a value of ETH Destination Addr Filter

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ DMAArbitration

| uint32_t ETH_DMAInitTypeDef::DMAArbitration |

Selects the DMA Tx/Rx arbitration. This parameter can be a value of ETH DMA Arbitration

Referenced by ETH_MACDMAConfig().

◆ DropTCPIPChecksumErrorFrame

| uint32_t ETH_DMAInitTypeDef::DropTCPIPChecksumErrorFrame |

Selects or not the Dropping of TCP/IP Checksum Error Frames. This parameter can be a value of ETH Drop TCP IP Checksum Error Frame

Referenced by ETH_MACDMAConfig().

◆ DuplexMode

| uint32_t ETH_InitTypeDef::DuplexMode |

Selects the MAC duplex mode: Half-Duplex or Full-Duplex mode This parameter can be a value of ETH Duplex Mode

Referenced by ETH_ConfigMAC(), and ethernetif_update_config().

◆ EnhancedDescriptorFormat

| uint32_t ETH_DMAInitTypeDef::EnhancedDescriptorFormat |

Enables the enhanced descriptor format. This parameter can be a value of ETH DMA Enhanced descriptor format

Referenced by ETH_MACDMAConfig().

◆ ExtendedStatus

| uint32_t ETH_DMADescTypeDef::ExtendedStatus |

Extended status for PTP receive descriptor

◆ FixedBurst

| uint32_t ETH_DMAInitTypeDef::FixedBurst |

Enables or disables the AHB Master interface fixed burst transfers. This parameter can be a value of ETH Fixed Burst

Referenced by ETH_MACDMAConfig().

◆ FlushReceivedFrame

| uint32_t ETH_DMAInitTypeDef::FlushReceivedFrame |

Enables or disables the flushing of received frames. This parameter can be a value of ETH Flush Received Frame

Referenced by ETH_MACDMAConfig().

◆ ForwardErrorFrames

| uint32_t ETH_DMAInitTypeDef::ForwardErrorFrames |

Selects or not the forward to the DMA of erroneous frames. This parameter can be a value of ETH Forward Error Frames

Referenced by ETH_MACDMAConfig().

◆ ForwardUndersizedGoodFrames

| uint32_t ETH_DMAInitTypeDef::ForwardUndersizedGoodFrames |

Enables or disables the Rx FIFO to forward Undersized frames (frames with no Error and length less than 64 bytes) including pad-bytes and CRC) This parameter can be a value of ETH Forward Undersized Good Frames

Referenced by ETH_MACDMAConfig().

◆ FSRxDesc

| ETH_DMADescTypeDef* ETH_DMARxFrameInfos::FSRxDesc |

First Segment Rx Desc

Referenced by low_level_input().

◆ HashTableHigh

| uint32_t ETH_MACInitTypeDef::HashTableHigh |

This field holds the higher 32 bits of Hash table. This parameter must be a number between Min_Data = 0x0 and Max_Data = 0xFFFFFFFFU

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ HashTableLow

| uint32_t ETH_MACInitTypeDef::HashTableLow |

This field holds the lower 32 bits of Hash table. This parameter must be a number between Min_Data = 0x0 and Max_Data = 0xFFFFFFFFU

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ Init

| ETH_InitTypeDef ETH_HandleTypeDef::Init |

Ethernet Init Configuration

Referenced by ETH_ConfigMAC(), ETH_DMARxDescListInit(), ETH_DMATxDescListInit(), ETH_MACDMAConfig(), ETH_ReadPHYRegister(), ETH_WritePHYRegister(), ethernetif_update_config(), HAL_ETH_DMATxDescListInit(), low_level_init(), and PHY_ETH_Init().

◆ Instance

| ETH_TypeDef* ETH_HandleTypeDef::Instance |

Register base address

Referenced by ETH_ConfigMAC(), ETH_DMAReceptionDisable(), ETH_DMAReceptionEnable(), ETH_DMARxDescListInit(), ETH_DMATransmissionDisable(), ETH_DMATransmissionEnable(), ETH_DMATxDescListInit(), ETH_FlushTransmitFIFO(), ETH_MACDMAConfig(), ETH_MACReceptionDisable(), ETH_MACReceptionEnable(), ETH_MACTransmissionDisable(), ETH_MACTransmissionEnable(), ETH_ReadPHYRegister(), ETH_TransmitFrame(), ETH_WritePHYRegister(), HAL_ETH_DMATxDescListInit(), low_level_init(), low_level_input(), low_level_output(), and PHY_ETH_Init().

◆ InterFrameGap

| uint32_t ETH_MACInitTypeDef::InterFrameGap |

Selects the minimum IFG between frames during transmission. This parameter can be a value of ETH Inter Frame Gap

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ Jabber

| uint32_t ETH_MACInitTypeDef::Jabber |

Selects or not Jabber timer When enabled, the MAC allows no more then 2048 bytes to be sent. When disabled, the MAC can send up to 16384 bytes. This parameter can be a value of ETH Jabber

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ length

| uint32_t ETH_DMARxFrameInfos::length |

Frame length

Referenced by ETH_GetReceivedFrame(), and low_level_input().

◆ LinkStatus

| uint32_t ETH_HandleTypeDef::LinkStatus |

Ethernet link status

◆ Lock

| LockTypeDef ETH_HandleTypeDef::Lock |

◆ LoopbackMode

| uint32_t ETH_MACInitTypeDef::LoopbackMode |

Selects or not the internal MAC MII Loopback mode. This parameter can be a value of ETH Loop Back Mode

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ LSRxDesc

| ETH_DMADescTypeDef* ETH_DMARxFrameInfos::LSRxDesc |

Last Segment Rx Desc

Referenced by ETH_GetReceivedFrame().

◆ MACAddr

| uint8_t* ETH_InitTypeDef::MACAddr |

MAC Address of used Hardware: must be pointer on an array of 6 bytes

Referenced by ETH_MACDMAConfig(), and low_level_init().

◆ MediaInterface

| uint32_t ETH_InitTypeDef::MediaInterface |

Selects the media-independent interface or the reduced media-independent interface. This parameter can be a value of ETH Media Interface

Referenced by low_level_init(), and PHY_ETH_Init().

◆ MulticastFramesFilter

| uint32_t ETH_MACInitTypeDef::MulticastFramesFilter |

Selects the Multicast Frames filter mode: None/HashTableFilter/PerfectFilter/PerfectHashTableFilter. This parameter can be a value of ETH Multicast Frames Filter

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ PassControlFrames

| uint32_t ETH_MACInitTypeDef::PassControlFrames |

Sets the forwarding mode of the control frames (including unicast and multicast PAUSE frames) This parameter can be a value of ETH Pass Control Frames

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ PauseLowThreshold

| uint32_t ETH_MACInitTypeDef::PauseLowThreshold |

This field configures the threshold of the PAUSE to be checked for automatic retransmission of PAUSE Frame. This parameter can be a value of ETH Pause Low Threshold

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ PauseTime

| uint32_t ETH_MACInitTypeDef::PauseTime |

This field holds the value to be used in the Pause Time field in the transmit control frame. This parameter must be a number between Min_Data = 0x0 and Max_Data = 0xFFFFU

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ PhyAddress

| uint16_t ETH_InitTypeDef::PhyAddress |

Ethernet PHY address. This parameter must be a number between Min_Data = 0 and Max_Data = 32

Referenced by ETH_ReadPHYRegister(), ETH_WritePHYRegister(), and low_level_init().

◆ PromiscuousMode

| uint32_t ETH_MACInitTypeDef::PromiscuousMode |

Selects or not the Promiscuous Mode This parameter can be a value of ETH Promiscuous Mode

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ ReceiveAll

| uint32_t ETH_MACInitTypeDef::ReceiveAll |

Selects or not all frames reception by the MAC (No filtering). This parameter can be a value of ETH Receive All

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ ReceiveFlowControl

| uint32_t ETH_MACInitTypeDef::ReceiveFlowControl |

Enables or disables the MAC to decode the received Pause frame and disable its transmitter for a specified time (Pause Time) This parameter can be a value of ETH Receive Flow Control

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ ReceiveOwn

| uint32_t ETH_MACInitTypeDef::ReceiveOwn |

Selects or not the ReceiveOwn, ReceiveOwn allows the reception of frames when the TX_EN signal is asserted in Half-Duplex mode. This parameter can be a value of ETH Receive Own

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ ReceiveStoreForward

| uint32_t ETH_DMAInitTypeDef::ReceiveStoreForward |

Enables or disables the Receive store and forward mode. This parameter can be a value of ETH Receive Store Forward

Referenced by ETH_MACDMAConfig().

◆ ReceiveThresholdControl

| uint32_t ETH_DMAInitTypeDef::ReceiveThresholdControl |

Selects the threshold level of the Receive FIFO. This parameter can be a value of ETH Receive Threshold Control

Referenced by ETH_MACDMAConfig().

◆ Reserved1

| uint32_t ETH_DMADescTypeDef::Reserved1 |

Reserved

◆ RetryTransmission

| uint32_t ETH_MACInitTypeDef::RetryTransmission |

Selects or not the MAC attempt retries transmission, based on the settings of BL, when a collision occurs (Half-Duplex mode). This parameter can be a value of ETH Retry Transmission

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ RxDesc

| ETH_DMADescTypeDef* ETH_HandleTypeDef::RxDesc |

Rx descriptor to Get

Referenced by ETH_DMARxDescListInit(), and ETH_GetReceivedFrame().

◆ RxDMABurstLength

| uint32_t ETH_DMAInitTypeDef::RxDMABurstLength |

Indicates the maximum number of beats to be transferred in one Rx DMA transaction. This parameter can be a value of ETH Rx DMA Burst Length

Referenced by ETH_MACDMAConfig().

◆ RxFrameInfos

| ETH_DMARxFrameInfos ETH_HandleTypeDef::RxFrameInfos |

last Rx frame infos

Referenced by ETH_GetReceivedFrame(), and low_level_input().

◆ RxMode

| uint32_t ETH_InitTypeDef::RxMode |

Selects the Ethernet Rx mode: Polling mode, Interrupt mode. This parameter can be a value of ETH Rx Mode

Referenced by low_level_init().

◆ SecondFrameOperate

| uint32_t ETH_DMAInitTypeDef::SecondFrameOperate |

Selects or not the Operate on second frame mode, which allows the DMA to process a second frame of Transmit data even before obtaining the status for the first frame. This parameter can be a value of ETH Second Frame Operate

Referenced by ETH_MACDMAConfig().

◆ SegCount

| uint32_t ETH_DMARxFrameInfos::SegCount |

Segment count

Referenced by low_level_input().

◆ SourceAddrFilter

| uint32_t ETH_MACInitTypeDef::SourceAddrFilter |

Selects the Source Address Filter mode. This parameter can be a value of ETH Source Addr Filter

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ Speed

| uint32_t ETH_InitTypeDef::Speed |

Sets the Ethernet speed: 10/100 Mbps. This parameter can be a value of ETH Speed

Referenced by ETH_ConfigMAC(), and ethernetif_update_config().

◆ State

| __IO ETH_StateTypeDef ETH_HandleTypeDef::State |

ETH communication state

Referenced by ETH_ConfigMAC(), ETH_DMARxDescListInit(), ETH_DMATxDescListInit(), ETH_GetReceivedFrame(), ETH_ReadPHYRegister(), ETH_Start(), ETH_Stop(), ETH_TransmitFrame(), ETH_WritePHYRegister(), HAL_ETH_DMATxDescListInit(), and PHY_ETH_Init().

◆ Status

| __IO uint32_t ETH_DMADescTypeDef::Status |

Status

Referenced by ETH_DMARxDescListInit(), ETH_DMATxDescListInit(), ETH_GetReceivedFrame(), ETH_TransmitFrame(), HAL_ETH_DMATxDescListInit(), and low_level_input().

◆ TimeStampHigh

| uint32_t ETH_DMADescTypeDef::TimeStampHigh |

Time Stamp High value for transmit and receive

◆ TimeStampLow

| uint32_t ETH_DMADescTypeDef::TimeStampLow |

Time Stamp Low value for transmit and receive

◆ TransmitFlowControl

| uint32_t ETH_MACInitTypeDef::TransmitFlowControl |

Enables or disables the MAC to transmit Pause frames (Full-Duplex mode) or the MAC back-pressure operation (Half-Duplex mode) This parameter can be a value of ETH Transmit Flow Control

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ TransmitStoreForward

| uint32_t ETH_DMAInitTypeDef::TransmitStoreForward |

Enables or disables Transmit store and forward mode. This parameter can be a value of ETH Transmit Store Forward

Referenced by ETH_MACDMAConfig().

◆ TransmitThresholdControl

| uint32_t ETH_DMAInitTypeDef::TransmitThresholdControl |

Selects or not the Transmit Threshold Control. This parameter can be a value of ETH Transmit Threshold Control

Referenced by ETH_MACDMAConfig().

◆ TxDesc

| ETH_DMADescTypeDef* ETH_HandleTypeDef::TxDesc |

Tx descriptor to Set

Referenced by ETH_DMATxDescListInit(), ETH_TransmitFrame(), HAL_ETH_DMATxDescListInit(), and low_level_output().

◆ TxDMABurstLength

| uint32_t ETH_DMAInitTypeDef::TxDMABurstLength |

Indicates the maximum number of beats to be transferred in one Tx DMA transaction. This parameter can be a value of ETH Tx DMA Burst Length

Referenced by ETH_MACDMAConfig().

◆ UnicastFramesFilter

| uint32_t ETH_MACInitTypeDef::UnicastFramesFilter |

Selects the Unicast Frames filter mode: HashTableFilter/PerfectFilter/PerfectHashTableFilter. This parameter can be a value of ETH Unicast Frames Filter

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ UnicastPauseFrameDetect

| uint32_t ETH_MACInitTypeDef::UnicastPauseFrameDetect |

Selects or not the MAC detection of the Pause frames (with MAC Address0 unicast address and unique multicast address). This parameter can be a value of ETH Unicast Pause Frame Detect

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ VLANTagComparison

| uint32_t ETH_MACInitTypeDef::VLANTagComparison |

Selects the 12-bit VLAN identifier or the complete 16-bit VLAN tag for comparison and filtering. This parameter can be a value of ETH VLAN Tag Comparison

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ VLANTagIdentifier

| uint32_t ETH_MACInitTypeDef::VLANTagIdentifier |

Holds the VLAN tag identifier for receive frames

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ Watchdog

| uint32_t ETH_MACInitTypeDef::Watchdog |

Selects or not the Watchdog timer When enabled, the MAC allows no more then 2048 bytes to be received. When disabled, the MAC can receive up to 16384 bytes. This parameter can be a value of ETH Watchdog

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().

◆ ZeroQuantaPause

| uint32_t ETH_MACInitTypeDef::ZeroQuantaPause |

Selects or not the automatic generation of Zero-Quanta Pause Control frames. This parameter can be a value of ETH Zero Quanta Pause

Referenced by ETH_ConfigMAC(), and ETH_MACDMAConfig().