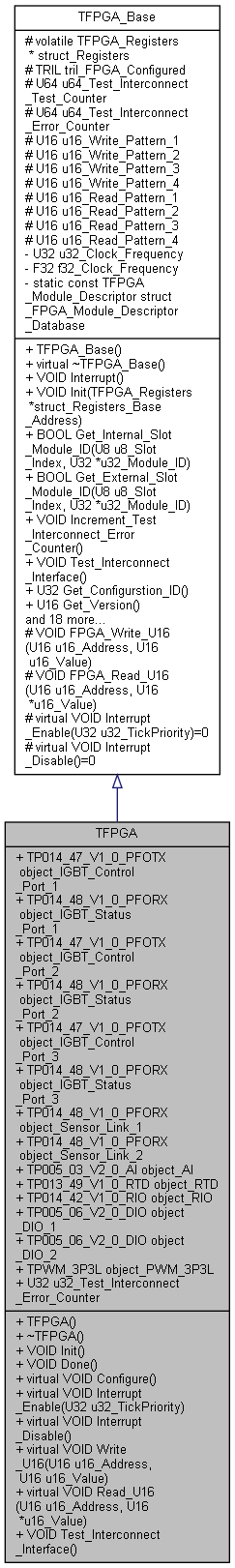

FPGA hardware abstraction level class. More...

#include <P014_49_V1_0_FPGA.h>

Public Member Functions | |

| TFPGA () | |

| FPGA object conctructor. More... | |

| ~TFPGA () | |

| FPGA object destructor. More... | |

| VOID | Init () |

| FPGA object initialization method. More... | |

| VOID | Done () |

| FPGA object finalisation method. More... | |

| virtual VOID | Configure () |

| Force load FPGA configuration from extern memory. More... | |

| virtual VOID | Interrupt_Enable (U32 u32_TickPriority) |

| Enable FPGA interrupt. More... | |

| virtual VOID | Interrupt_Disable () |

| Disable FPGA interrupt. More... | |

| virtual VOID | Write_U16 (U16 u16_Address, U16 u16_Value) |

| Write U16 value into FPGA using generic access. More... | |

| virtual VOID | Read_U16 (U16 u16_Address, U16 *u16_Value) |

| Read U16 value from FPGA using generic access. More... | |

| VOID | Test_Interconnect_Interface () |

Public Member Functions inherited from TFPGA_Base Public Member Functions inherited from TFPGA_Base | |

| TFPGA_Base () | |

| FPGA base class constructor method. More... | |

| virtual | ~TFPGA_Base () |

| FPGA base class destructor method. More... | |

| VOID | Interrupt () |

| FPGA interrupt method. More... | |

| VOID | Init (TFPGA_Registers *struct_Registers_Base_Address) |

| FPGA object initialisation method. More... | |

| BOOL | Get_Internal_Slot_Module_ID (U8 u8_Slot_Index, U32 *u32_Module_ID) |

| BOOL | Get_External_Slot_Module_ID (U8 u8_Slot_Index, U32 *u32_Module_ID) |

| VOID | Increment_Test_Interconnect_Error_Counter () |

| Increment test interconnect error counter method. More... | |

| VOID | Test_Interconnect_Interface () |

| Check FPGA interconnection interface method. More... | |

| U32 | Get_Configurstion_ID () |

| Get FPGA configuration ID method. More... | |

| U16 | Get_Version () |

| Get FPGA configuration version method. More... | |

| U16 | Get_Revision () |

| Get FPGA configuration revision method. More... | |

| U32 | Get_Clock_Frequency () |

| Get FPGA clock frequency in herz method. More... | |

| U16 | Get_Slot_Size () |

| Get FPGA slot size method. More... | |

| F32 | Get_Clock_Frequency_In_Hz () |

| Get FPGA internal clock frequency in Hz method. More... | |

| U64 | Get_Interconnect_Error_Count () |

| Get FPGA interconnect error count method. More... | |

| U64 | Get_Interconnect_Test_Count () |

| Get FPGA interconnect test count method. More... | |

| virtual BOOL | Is_Installed () |

| Get FPGA init status method. More... | |

| TRIL | Is_Configured () |

| Return FPGA configuration status method. More... | |

| virtual BOOL | FPGA_PROG_Pin_Status ()=0 |

| Get FPGA PROG pin status method. More... | |

| virtual BOOL | FPGA_DONE_Pin_Status ()=0 |

| Get FPGA DONE pin status method. More... | |

| VOID | Send_General_Information (TProtocol_Base *object_Protocol) |

| Send general information about FPGA object. More... | |

| VOID | Send_Internal_Slot_Information (TProtocol_Base *object_Protocol) |

| Send information about internal slots allocation. More... | |

| VOID | Send_External_Slot_Information (TProtocol_Base *object_Protocol) |

| Send information about external slots allocation. More... | |

| VOID | Reset_Watchdog () |

| Reset FPGA watchdog. More... | |

| BOOL | Get_Slot_Module_Name_By_ID (U32 u32_Module_ID, C8 **c8_Module_Name) |

| VOID | Send_Internal_Module_Information (U8 u8_Slot, TProtocol_Base *object_Protocol) |

| VOID | Send_External_Module_Information (U8 u8_Slot, TProtocol_Base *object_Protocol) |

Additional Inherited Members | |

Protected Member Functions inherited from TFPGA_Base Protected Member Functions inherited from TFPGA_Base | |

| VOID | FPGA_Write_U16 (U16 u16_Address, U16 u16_Value) |

| Write U16 value into FPGA using generic access. More... | |

| VOID | FPGA_Read_U16 (U16 u16_Address, U16 *u16_Value) |

| Read U16 value from FPGA using generic access. More... | |

Protected Attributes inherited from TFPGA_Base Protected Attributes inherited from TFPGA_Base | |

| volatile TFPGA_Registers * | struct_Registers = (TFPGA_Registers*)NULL |

| Mapped FPGA registers. More... | |

| TRIL | tril_FPGA_Configured = (TRIL)unset |

| FPGA configuration status. More... | |

| U64 | u64_Test_Interconnect_Test_Counter = (U64)0 |

| Interconnect test counter. More... | |

| U64 | u64_Test_Interconnect_Error_Counter = (U64)0 |

| Interconnect error counter for diagnose. More... | |

| U16 | u16_Write_Pattern_1 |

| Write pattern #1 for testng. More... | |

| U16 | u16_Write_Pattern_2 |

| Write pattern #2 for testng. More... | |

| U16 | u16_Write_Pattern_3 |

| Write pattern #3 for testng. More... | |

| U16 | u16_Write_Pattern_4 |

| Write pattern #4 for testng. More... | |

| U16 | u16_Read_Pattern_1 |

| Reading pattern #1 for testng. More... | |

| U16 | u16_Read_Pattern_2 |

| Reading pattern #2 for testng. More... | |

| U16 | u16_Read_Pattern_3 |

| Reading pattern #3 for testng. More... | |

| U16 | u16_Read_Pattern_4 |

| Reading pattern #4 for testng. More... | |

Detailed Description

FPGA hardware abstraction level class.

Constructor & Destructor Documentation

◆ TFPGA()

| TFPGA::TFPGA | ( | ) |

FPGA object conctructor.

- Returns

- Pointer to the object

- Note

- Note

◆ ~TFPGA()

| TFPGA::~TFPGA | ( | ) |

FPGA object destructor.

- Returns

- None

- Note

- None

Member Function Documentation

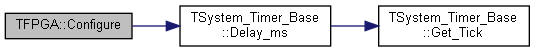

◆ Configure()

|

virtual |

Force load FPGA configuration from extern memory.

- Returns

- None

- Note

- None

Implements TFPGA_Base.

References TSystem_Timer_Base::Delay_ms(), and object_System_Timer.

◆ Done()

| VOID TFPGA::Done | ( | ) |

FPGA object finalisation method.

- Returns

- None

- Note

- None

References Interrupt_Disable().

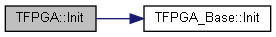

◆ Init()

| VOID TFPGA::Init | ( | ) |

FPGA object initialization method.

- Returns

- None

- Note

- None

References FPGA_BASE, TFPGA_Base::Init(), and u32_Test_Interconnect_Error_Counter.

◆ Interrupt_Disable()

|

virtual |

Disable FPGA interrupt.

- Returns

- None

- Note

- None

Implements TFPGA_Base.

Referenced by Done().

◆ Interrupt_Enable()

◆ Read_U16()

Read U16 value from FPGA using generic access.

- Parameters

-

[in] u16_Address Logical address for read operation. [out] u16_Value Readed U16 value from FPGA.

- Returns

- None

- Note

- None

References TFPGA_Base::struct_Registers, and TFPGA_Base::TFPGA_Registers::u16_Data.

◆ Test_Interconnect_Interface()

| VOID TFPGA::Test_Interconnect_Interface | ( | ) |

References object_Delay_Timer, TFPGA_Base::struct_Registers, TFPGA_Base::TFPGA_Registers::u16_Test_Register_1, TFPGA_Base::TFPGA_Registers::u16_Test_Register_2, TFPGA_Base::TFPGA_Registers::u16_Test_Register_3, TFPGA_Base::TFPGA_Registers::u16_Test_Register_4, and u32_Test_Interconnect_Error_Counter.

◆ Write_U16()

Write U16 value into FPGA using generic access.

- Parameters

-

[in] u16_Address Logical address for read operation. [in] u16_Value U16 value for write into FPGA.

- Returns

- None

- Note

- None

References TFPGA_Base::struct_Registers, and TFPGA_Base::TFPGA_Registers::u16_Data.

Member Data Documentation

◆ object_AI

| TP005_03_V2_0_AI TFPGA::object_AI |

◆ object_DIO_1

| TP005_06_V2_0_DIO TFPGA::object_DIO_1 |

◆ object_DIO_2

| TP005_06_V2_0_DIO TFPGA::object_DIO_2 |

◆ object_IGBT_Control_Port_1

| TP014_47_V1_0_PFOTX TFPGA::object_IGBT_Control_Port_1 |

◆ object_IGBT_Control_Port_2

| TP014_47_V1_0_PFOTX TFPGA::object_IGBT_Control_Port_2 |

◆ object_IGBT_Control_Port_3

| TP014_47_V1_0_PFOTX TFPGA::object_IGBT_Control_Port_3 |

◆ object_IGBT_Status_Port_1

| TP014_48_V1_0_PFORX TFPGA::object_IGBT_Status_Port_1 |

◆ object_IGBT_Status_Port_2

| TP014_48_V1_0_PFORX TFPGA::object_IGBT_Status_Port_2 |

◆ object_IGBT_Status_Port_3

| TP014_48_V1_0_PFORX TFPGA::object_IGBT_Status_Port_3 |

◆ object_PWM_3P3L

| TPWM_3P3L TFPGA::object_PWM_3P3L |

◆ object_RIO

| TP014_42_V1_0_RIO TFPGA::object_RIO |

◆ object_RTD

| TP013_49_V1_0_RTD TFPGA::object_RTD |

◆ object_Sensor_Link_1

| TP014_48_V1_0_PFORX TFPGA::object_Sensor_Link_1 |

◆ object_Sensor_Link_2

| TP014_48_V1_0_PFORX TFPGA::object_Sensor_Link_2 |

◆ u32_Test_Interconnect_Error_Counter

| U32 TFPGA::u32_Test_Interconnect_Error_Counter |

Referenced by Init(), and Test_Interconnect_Interface().

The documentation for this class was generated from the following files:

- ConOpSys/Hardware/P014_49_V1_0_CB/P014_49_V1_0_FPGA.h

- ConOpSys/Hardware/P014_49_V1_0_CB/P014_49_V1_0_FPGA.cpp