KG3 RTD input board P017.41 hardware driver implementation file. More...

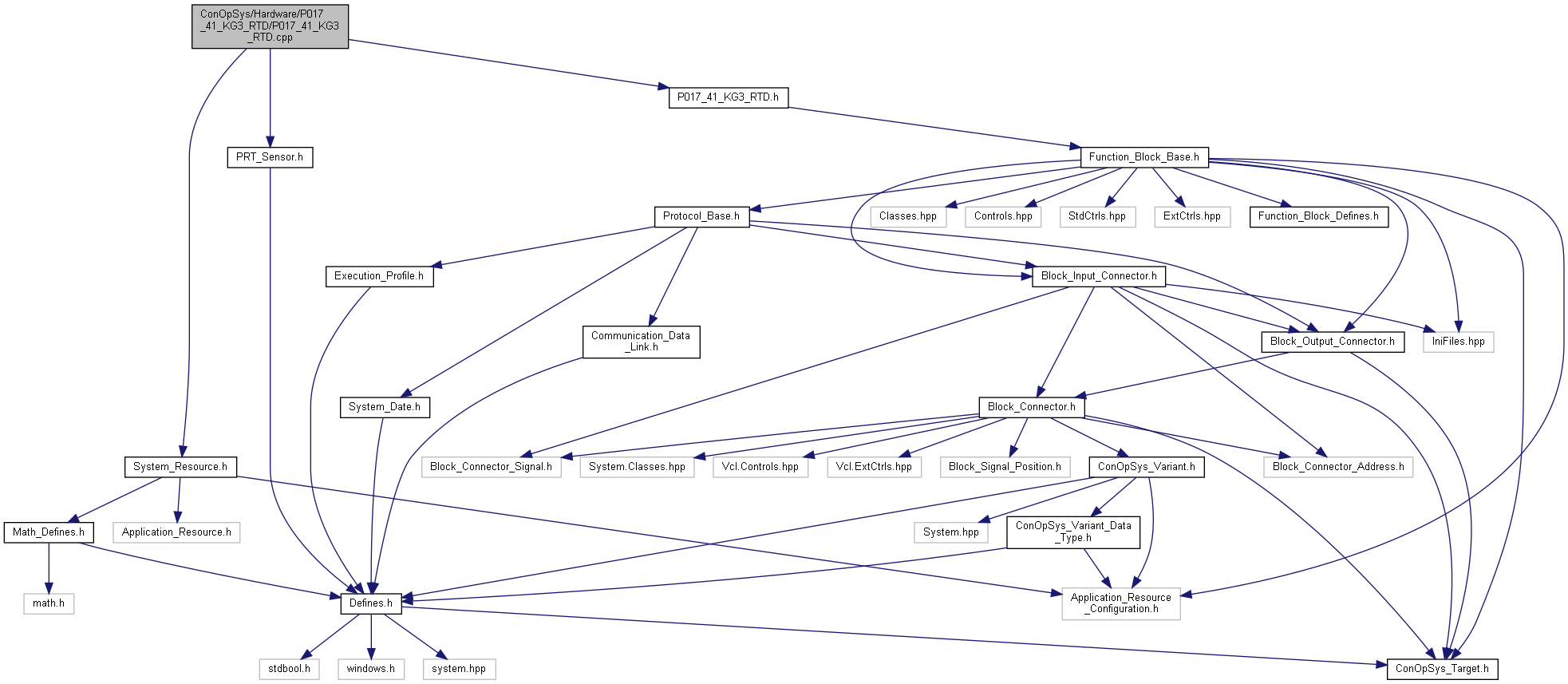

Include dependency graph for P017_41_KG3_RTD.cpp:

Detailed Description

KG3 RTD input board P017.41 hardware driver implementation file.

- Attention

- No special attention requered.

- Copyright

- (C) 2015-2020 ANVILEX LLC $HeadURL: https://192.168.3.4:8443/svn/P004_07/ConOpSys/Hardware/P017_41_KG3_RTD/P017_41_KG3_RTD.cpp $

- Revision

- 2855

- Date

- 2021-08-23 21:04:19 +0500 (Mo, 23 Aug 2021)

- Author

- ggavrituhin

Macro Definition Documentation

◆ RTD_CHANNEL_1_CONFIGURATION_WORD

| #define RTD_CHANNEL_1_CONFIGURATION_WORD ((U16)0x00C3) |

◆ RTD_CHANNEL_1_FAULT_RESET_WORD

| #define RTD_CHANNEL_1_FAULT_RESET_WORD ((U16)0x00C3) |

◆ RTD_CHANNEL_1_READ_CONFIGURATION

| #define RTD_CHANNEL_1_READ_CONFIGURATION ((U16)0x4000) |

◆ RTD_CHANNEL_1_READ_FAULT_STATUS

| #define RTD_CHANNEL_1_READ_FAULT_STATUS ((U16)0x4007) |

◆ RTD_CHANNEL_1_READ_HIGH_FAULT_THRESHOLD

| #define RTD_CHANNEL_1_READ_HIGH_FAULT_THRESHOLD ((U16)0x0003) |

◆ RTD_CHANNEL_1_READ_HIGH_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_1_READ_HIGH_FAULT_THRESHOLD_LSB ((U16)0x4004) |

◆ RTD_CHANNEL_1_READ_HIGH_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_1_READ_HIGH_FAULT_THRESHOLD_MSB ((U16)0x4003) |

◆ RTD_CHANNEL_1_READ_LOW_FAULT_THRESHOLD

| #define RTD_CHANNEL_1_READ_LOW_FAULT_THRESHOLD ((U16)0x0005) |

◆ RTD_CHANNEL_1_READ_LOW_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_1_READ_LOW_FAULT_THRESHOLD_LSB ((U16)0x4006) |

◆ RTD_CHANNEL_1_READ_LOW_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_1_READ_LOW_FAULT_THRESHOLD_MSB ((U16)0x4005) |

◆ RTD_CHANNEL_1_READ_TEMPERATURE

| #define RTD_CHANNEL_1_READ_TEMPERATURE ((U16)0x0001) |

◆ RTD_CHANNEL_1_READ_TEMPERATURE_LSB

| #define RTD_CHANNEL_1_READ_TEMPERATURE_LSB ((U16)0x4002) |

◆ RTD_CHANNEL_1_READ_TEMPERATURE_MSB

| #define RTD_CHANNEL_1_READ_TEMPERATURE_MSB ((U16)0x4001) |

◆ RTD_CHANNEL_1_WRITE_CONFIGURATION

| #define RTD_CHANNEL_1_WRITE_CONFIGURATION ((U16)0xC000) |

◆ RTD_CHANNEL_1_WRITE_HIGH_FAULT_THRESHOLD

| #define RTD_CHANNEL_1_WRITE_HIGH_FAULT_THRESHOLD ((U16)0x8003) |

◆ RTD_CHANNEL_1_WRITE_HIGH_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_1_WRITE_HIGH_FAULT_THRESHOLD_LSB ((U16)0xC004) |

◆ RTD_CHANNEL_1_WRITE_HIGH_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_1_WRITE_HIGH_FAULT_THRESHOLD_MSB ((U16)0xC003) |

◆ RTD_CHANNEL_1_WRITE_LOW_FAULT_THRESHOLD

| #define RTD_CHANNEL_1_WRITE_LOW_FAULT_THRESHOLD ((U16)0x8005) |

◆ RTD_CHANNEL_1_WRITE_LOW_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_1_WRITE_LOW_FAULT_THRESHOLD_LSB ((U16)0xC006) |

◆ RTD_CHANNEL_1_WRITE_LOW_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_1_WRITE_LOW_FAULT_THRESHOLD_MSB ((U16)0xC005) |

◆ RTD_CHANNEL_2_CONFIGURATION_WORD

| #define RTD_CHANNEL_2_CONFIGURATION_WORD ((U16)0x00C3) |

◆ RTD_CHANNEL_2_FAULT_RESET_WORD

| #define RTD_CHANNEL_2_FAULT_RESET_WORD ((U16)0x00C3) |

◆ RTD_CHANNEL_2_READ_CONFIGURATION

| #define RTD_CHANNEL_2_READ_CONFIGURATION ((U16)0x4008) |

◆ RTD_CHANNEL_2_READ_FAULT_STATUS

| #define RTD_CHANNEL_2_READ_FAULT_STATUS ((U16)0x400F) |

◆ RTD_CHANNEL_2_READ_HIGH_FAULT_THRESHOLD

| #define RTD_CHANNEL_2_READ_HIGH_FAULT_THRESHOLD ((U16)0x000B) |

◆ RTD_CHANNEL_2_READ_HIGH_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_2_READ_HIGH_FAULT_THRESHOLD_LSB ((U16)0x400C) |

◆ RTD_CHANNEL_2_READ_HIGH_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_2_READ_HIGH_FAULT_THRESHOLD_MSB ((U16)0x400B) |

◆ RTD_CHANNEL_2_READ_LOW_FAULT_THRESHOLD

| #define RTD_CHANNEL_2_READ_LOW_FAULT_THRESHOLD ((U16)0x000D) |

◆ RTD_CHANNEL_2_READ_LOW_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_2_READ_LOW_FAULT_THRESHOLD_LSB ((U16)0x400E) |

◆ RTD_CHANNEL_2_READ_LOW_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_2_READ_LOW_FAULT_THRESHOLD_MSB ((U16)0x400D) |

◆ RTD_CHANNEL_2_READ_TEMPERATURE

| #define RTD_CHANNEL_2_READ_TEMPERATURE ((U16)0x0009) |

◆ RTD_CHANNEL_2_READ_TEMPERATURE_LSB

| #define RTD_CHANNEL_2_READ_TEMPERATURE_LSB ((U16)0x400A) |

◆ RTD_CHANNEL_2_READ_TEMPERATURE_MSB

| #define RTD_CHANNEL_2_READ_TEMPERATURE_MSB ((U16)0x4009) |

◆ RTD_CHANNEL_2_WRITE_CONFIGURATION

| #define RTD_CHANNEL_2_WRITE_CONFIGURATION ((U16)0xC008) |

◆ RTD_CHANNEL_2_WRITE_HIGH_FAULT_THRESHOLD

| #define RTD_CHANNEL_2_WRITE_HIGH_FAULT_THRESHOLD ((U16)0x800B) |

◆ RTD_CHANNEL_2_WRITE_HIGH_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_2_WRITE_HIGH_FAULT_THRESHOLD_LSB ((U16)0xC00C) |

◆ RTD_CHANNEL_2_WRITE_HIGH_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_2_WRITE_HIGH_FAULT_THRESHOLD_MSB ((U16)0xC00B) |

◆ RTD_CHANNEL_2_WRITE_LOW_FAULT_THRESHOLD

| #define RTD_CHANNEL_2_WRITE_LOW_FAULT_THRESHOLD ((U16)0x800D) |

◆ RTD_CHANNEL_2_WRITE_LOW_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_2_WRITE_LOW_FAULT_THRESHOLD_LSB ((U16)0xC00E) |

◆ RTD_CHANNEL_2_WRITE_LOW_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_2_WRITE_LOW_FAULT_THRESHOLD_MSB ((U16)0xC00D) |

◆ RTD_CHANNEL_3_CONFIGURATION_WORD

| #define RTD_CHANNEL_3_CONFIGURATION_WORD ((U16)0x00C3) |

◆ RTD_CHANNEL_3_FAULT_RESET_WORD

| #define RTD_CHANNEL_3_FAULT_RESET_WORD ((U16)0x00C3) |

◆ RTD_CHANNEL_3_READ_CONFIGURATION

| #define RTD_CHANNEL_3_READ_CONFIGURATION ((U16)0x4010) |

◆ RTD_CHANNEL_3_READ_FAULT_STATUS

| #define RTD_CHANNEL_3_READ_FAULT_STATUS ((U16)0x4017) |

◆ RTD_CHANNEL_3_READ_HIGH_FAULT_THRESHOLD

| #define RTD_CHANNEL_3_READ_HIGH_FAULT_THRESHOLD ((U16)0x0013) |

◆ RTD_CHANNEL_3_READ_HIGH_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_3_READ_HIGH_FAULT_THRESHOLD_LSB ((U16)0x4014) |

◆ RTD_CHANNEL_3_READ_HIGH_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_3_READ_HIGH_FAULT_THRESHOLD_MSB ((U16)0x4013) |

◆ RTD_CHANNEL_3_READ_LOW_FAULT_THRESHOLD

| #define RTD_CHANNEL_3_READ_LOW_FAULT_THRESHOLD ((U16)0x0015) |

◆ RTD_CHANNEL_3_READ_LOW_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_3_READ_LOW_FAULT_THRESHOLD_LSB ((U16)0x4016) |

◆ RTD_CHANNEL_3_READ_LOW_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_3_READ_LOW_FAULT_THRESHOLD_MSB ((U16)0x4015) |

◆ RTD_CHANNEL_3_READ_TEMPERATURE

| #define RTD_CHANNEL_3_READ_TEMPERATURE ((U16)0x0011) |

◆ RTD_CHANNEL_3_READ_TEMPERATURE_LSB

| #define RTD_CHANNEL_3_READ_TEMPERATURE_LSB ((U16)0x4012) |

◆ RTD_CHANNEL_3_READ_TEMPERATURE_MSB

| #define RTD_CHANNEL_3_READ_TEMPERATURE_MSB ((U16)0x4011) |

◆ RTD_CHANNEL_3_WRITE_CONFIGURATION

| #define RTD_CHANNEL_3_WRITE_CONFIGURATION ((U16)0xC010) |

◆ RTD_CHANNEL_3_WRITE_HIGH_FAULT_THRESHOLD

| #define RTD_CHANNEL_3_WRITE_HIGH_FAULT_THRESHOLD ((U16)0x8013) |

◆ RTD_CHANNEL_3_WRITE_HIGH_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_3_WRITE_HIGH_FAULT_THRESHOLD_LSB ((U16)0xC014) |

◆ RTD_CHANNEL_3_WRITE_HIGH_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_3_WRITE_HIGH_FAULT_THRESHOLD_MSB ((U16)0xC013) |

◆ RTD_CHANNEL_3_WRITE_LOW_FAULT_THRESHOLD

| #define RTD_CHANNEL_3_WRITE_LOW_FAULT_THRESHOLD ((U16)0x8015) |

◆ RTD_CHANNEL_3_WRITE_LOW_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_3_WRITE_LOW_FAULT_THRESHOLD_LSB ((U16)0xC016) |

◆ RTD_CHANNEL_3_WRITE_LOW_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_3_WRITE_LOW_FAULT_THRESHOLD_MSB ((U16)0xC015) |

◆ RTD_CHANNEL_4_CONFIGURATION_WORD

| #define RTD_CHANNEL_4_CONFIGURATION_WORD ((U16)0x00C3) |

◆ RTD_CHANNEL_4_FAULT_RESET_WORD

| #define RTD_CHANNEL_4_FAULT_RESET_WORD ((U16)0x00C3) |

◆ RTD_CHANNEL_4_READ_CONFIGURATION

| #define RTD_CHANNEL_4_READ_CONFIGURATION ((U16)0x4018) |

◆ RTD_CHANNEL_4_READ_FAULT_STATUS

| #define RTD_CHANNEL_4_READ_FAULT_STATUS ((U16)0x401F) |

◆ RTD_CHANNEL_4_READ_HIGH_FAULT_THRESHOLD

| #define RTD_CHANNEL_4_READ_HIGH_FAULT_THRESHOLD ((U16)0x001B) |

◆ RTD_CHANNEL_4_READ_HIGH_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_4_READ_HIGH_FAULT_THRESHOLD_LSB ((U16)0x401C) |

◆ RTD_CHANNEL_4_READ_HIGH_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_4_READ_HIGH_FAULT_THRESHOLD_MSB ((U16)0x401B) |

◆ RTD_CHANNEL_4_READ_LOW_FAULT_THRESHOLD

| #define RTD_CHANNEL_4_READ_LOW_FAULT_THRESHOLD ((U16)0x001D) |

◆ RTD_CHANNEL_4_READ_LOW_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_4_READ_LOW_FAULT_THRESHOLD_LSB ((U16)0x401E) |

◆ RTD_CHANNEL_4_READ_LOW_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_4_READ_LOW_FAULT_THRESHOLD_MSB ((U16)0x401D) |

◆ RTD_CHANNEL_4_READ_TEMPERATURE

| #define RTD_CHANNEL_4_READ_TEMPERATURE ((U16)0x0019) |

◆ RTD_CHANNEL_4_READ_TEMPERATURE_LSB

| #define RTD_CHANNEL_4_READ_TEMPERATURE_LSB ((U16)0x401A) |

◆ RTD_CHANNEL_4_READ_TEMPERATURE_MSB

| #define RTD_CHANNEL_4_READ_TEMPERATURE_MSB ((U16)0x4019) |

◆ RTD_CHANNEL_4_WRITE_CONFIGURATION

| #define RTD_CHANNEL_4_WRITE_CONFIGURATION ((U16)0xC018) |

◆ RTD_CHANNEL_4_WRITE_HIGH_FAULT_THRESHOLD

| #define RTD_CHANNEL_4_WRITE_HIGH_FAULT_THRESHOLD ((U16)0x801B) |

◆ RTD_CHANNEL_4_WRITE_HIGH_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_4_WRITE_HIGH_FAULT_THRESHOLD_LSB ((U16)0xC01C) |

◆ RTD_CHANNEL_4_WRITE_HIGH_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_4_WRITE_HIGH_FAULT_THRESHOLD_MSB ((U16)0xC01B) |

◆ RTD_CHANNEL_4_WRITE_LOW_FAULT_THRESHOLD

| #define RTD_CHANNEL_4_WRITE_LOW_FAULT_THRESHOLD ((U16)0x801D) |

◆ RTD_CHANNEL_4_WRITE_LOW_FAULT_THRESHOLD_LSB

| #define RTD_CHANNEL_4_WRITE_LOW_FAULT_THRESHOLD_LSB ((U16)0xC01E) |

◆ RTD_CHANNEL_4_WRITE_LOW_FAULT_THRESHOLD_MSB

| #define RTD_CHANNEL_4_WRITE_LOW_FAULT_THRESHOLD_MSB ((U16)0xC01D) |

◆ RTD_STATUS_REGISTER_READY_BIT

| #define RTD_STATUS_REGISTER_READY_BIT ((U16)0x2000) |